基于FPGA和单片机的频率监测系统

O.引言

本系统利用单片机和FPGA有效的结合起来共同实现等精度频率测量和IDDS技术,发挥各自的优点,使设计变得更加容易和灵活,并具有频率测量范围宽、产生的波形频率分辨率高及精度大等特点。

系统方便灵活,测量精度和产生的波形分辨率高,能适应当代许多高精度测量和波形产生的要求,可以在各类测量系统和信号发生器中得到很好的利用,频率测量在电路实验、通讯设备、音频视频和科学研究中具有十分广泛的用途。等精度测量技术具有广阔的应用前景,由于其性能的优越性,在目前各个测量领域中都可以发挥着很好的作用,特别是在海洋勘探,太空探索以及各类实验中都得到了应用。

1.DDS信号发生器的实现

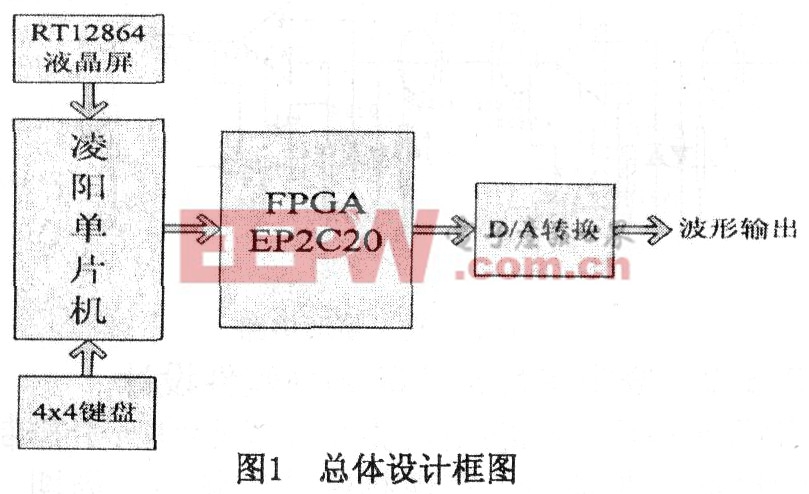

使用FPGA与单片机相结合的方式构成DDS信号发生器的核心部分,这是一种从相位概念出发直接合成所需波形的一种新的全数字频率合成技术。其中FPGA完成相位累加、波形地址查找及波形输出等功能,凌阳16位单片机实现频率控制字的输入和液晶显示部分。FPGA与单片机通过串行输入并行输出的方式进行通信。其总体设计框图如图1所示。

1.1 DDS产生原理

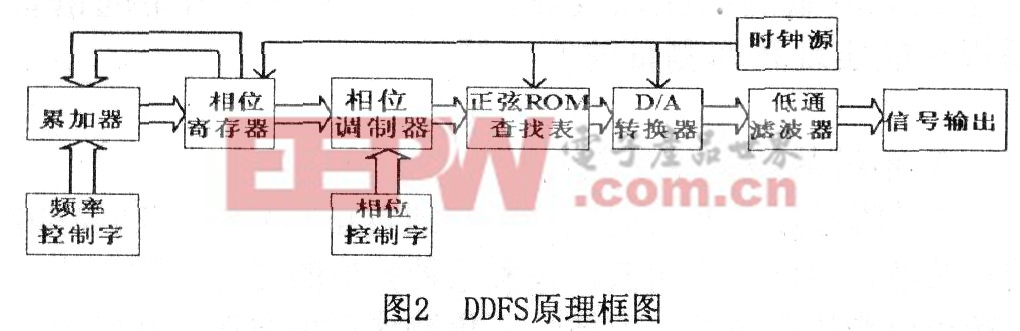

图2是一个基本的DDFS结构框图。DDFS 以数控振荡器的方式,产生频率可控制的正弦波、方波、三角波,电路包括了基准时钟源、相位累加器、相位调制器、波形ROM查找表、D/A转换器和低通滤波器等。频率控制字N和相位控制字M分别控制DDS所输出的波形的频率和正弦波的相位。

1.1.1 频率部分

一个N位字长的二进制加法器的一端和一个固定时钟脉冲取样的N位相位寄存器相连,另一个输入端是外部输入的控制字M。这样在每一个时钟到来的时候,前一次相位寄存器中的值和当前的M值相加,作为当前相位寄存器的输出。控制字M决定了相位增量,加法器不断的对相位增量进行线性累加。当产生一次溢出后,完成一个周期性动作,即DDFS合成信号的一个频率周期。

设基准时钟信号为fclk,分频值为N,累加器位数为M,相位累加器步进值为L,根据公式:

设最高频率为20KHz,步进为20Hz,因此累加器位数至少为10位(210=1024>20000/20)。为了保证在最高频率下的波形在一个周期内至少有32个点,因此累加器至少有lO+5=15位。

取晶振频率32.768MHz,可得

1.1.2 相位部分

相位寄存器的输出通过相位调制器与相位控制字K相加,使最终的输出产生一定的相位偏移θ,θ的值与相位控制字K与ROM中的数据有关。我们通过设置两路信号的K值,使两路信号有不同的相位偏移量,从而产生相位差△θ。设A路信号的控制字为K,B路信号的控制字为K’,考虑到FPGA的内部资源,取512个采样点,可得

通常我们只要改变控制字K就可以实现步进调整。

评论