基于AT89S52和ATF1508AS的LED显示屏的硬件设计

0 引言

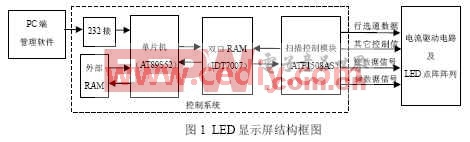

LED显示屏主要由电流驱动电路及LED点阵阵列、控制系统和PC端管理软件三部分构成(图1)。控制系统负责接收、转换和处理各种外部信号,并实现扫描控制,然后驱动LED点阵显示需要的文字或图案。控制系统作为LED显示屏的核心部分,直接决定了显示屏的显示效果和性能的优劣。本文详细分析采用Verilog HDL对ATF1508AS进行编程,实现双口RAM访问和产生LED点阵驱动电路所需的各种时序信号。

1 LED显示屏的基本结构及关键技术

本系统设计中,控制系统采用单片机+CPLD的方案来实现,整个控制系统可分为:信号接收及处理模块和CPLD的扫描控制模块和LED点阵驱动模块,如图1 所示。本系统的关键技术是使用双口RAM和CPLD芯片,解决LED显示屏中高速数据传输和快速扫描控制的难题,大大提高了动态显示的刷新率。

信号接收与处理模块的功能是AT89S52单片机通过串口接收PC送来的点阵信息,同时对点阵信息做各种不同的处理。利用双口RAM IDT7007在单片机和ATF1508AS之间以共享的方式建立高速的数据交换通道。

CPLD的扫描控制模块采用ATF1508AS芯片实现。其功能是从双口RAM读取点阵信息,串行化后送显示扫描驱动电路,同时输出各种所需的控制信号。CPLD具有扫描速度快,延时短等特点,克服了单片机由于传输速率慢而造成在大屏幕显示时产生的闪烁效应。

2 基于CPLD的扫描控制模块的设计

2.1 设计思想

本模块的功能是从存储器中读取数据,将数据输送到显示屏体上,同时产生各种控制信号。时序产生模块由两部分构成,一是产生访问双口RAM的时序,二是产生LED显示屏接口所需的各种信号。

硬件电路我们采用较常见的CPLD芯片ATF1508来实现控制系统中的时序产生部分。CPLD是一种具有丰富的可变成I/O引脚的可编程逻辑器件,不仅可以实现常规的逻辑器件功能,还可以实现复杂而独特的时序逻辑功能。软件我们采用Verilog HDL语言来进行设计。Verilog HDL是用于逻辑设计的硬件描述语言,已成为IEEE标准。利用Verilog HDL语言对ATF1508AS进行编程,实现扫描控制模块所需的功能。

扫描控制部分的原理电路如图2所示,ATF1508AS是核心部分,需要根据系统需要定义ATF1508AS的各个I/O端口,下面是I/O端口定义和内部寄存器定义的Verilog HDL语言代码。

module LedSequ(color, datain, addrout, CE, OE, SEMR, RWC, sdr, sdb, sck, le, oe1, cs, clk, counter);

input clk; //系统时钟

input[7:0] datain;//RAM数据输入

input[1:0] color;//颜色控制

output[13:0] addrout;//地址输出口

output SEMR,RWC;

output CE,OE,sdr,sdb,sck,le,oe1,cs;

output[3:0] counter;

reg[3:0] hcnt;//38译码器计数器

reg [7:0] data1;//数据寄存器

reg[3:0] counter;//38翻码器输出端

reg SEMR,RWC;

reg SDA,SDC;

评论