ARM中基于DMA的高效UART通讯及其应用

1、引言

本文引用地址:http://www.amcfsurvey.com/article/171609.htm由于UART串行口的广泛应用,在传统的8位和16位的处理器以及32位处理器中,一般都带有UART串行口。传统的基于UART的数据通讯中,采用的方式一般有两种,查询式和中断式。查询方式下CPU的负担较重,浪费了处理器的能力,不能够很好的处理其他的事件;中断方式可以在接收到信息或需要发送数据时产生中断,在中断服务程序中完成数据的接收与发送。相对于查询方式,中断方式的CPU利用率要高。在CPU任务简单的系统中,使用中断方式确实是一种好方法。但是在复杂的系统中,比如移动机器人,处理器需要处理串行口通信,多个传感器数据的采集以及处理,实时轨迹的生成,运动轨迹插补以及位置闭环控制等等任务,牵扯到多个中断的优先级分配问题。为了保证数据发送与接收的可靠性,需要把UART的中断优先级设计较高,但是系统可能还有其他的需要更高优先级的中断,必须保证其定时的准确,这样就有可能造成串行通讯的中断不能及时响应,从而造成数据丢失。为此,笔者在采用S3c44b0x设计移动机器人控制器时,为了保证串行通讯的数据及时可靠的接收,同时兼顾其它任务不受影响,采用了基于DMA和中断方式相结合的UART串行通信方式。DMA是 Direct Memory Access的缩写,意思是“存储器直接访问”,它是一种高速的数据传输操作,允许在外部设备和存储器之间直接读/写数据,即不通过CPU,也不需要 CPU干预。整个数据传输操作是在一个称作DMA控制器的控制下进行的。CPU除了在数据传输开始和结束时做一点处理外,在传输过程中可以进行其他的工作。这样,在大部分时间里,CPU和输入/输出设备都处于并行的操作状态。其基本原理可以查阅教科书,此处不赘述。这里仅介绍S3c44c0x的DMA控制器。

2、S3c44b0x中的DMA控制器和UART的特性

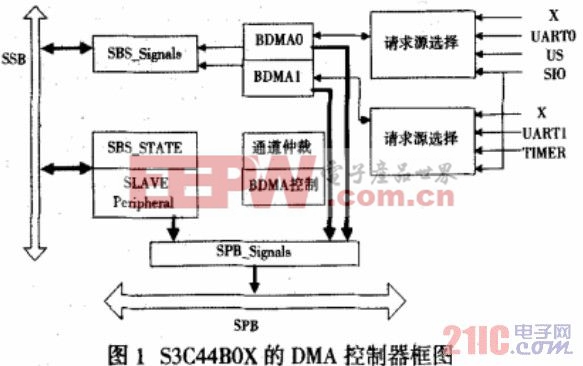

S3c44b0x采用ARM7TDMI核,具有4 通道的DMA控制器,并且对应有4个中断。其中两个DMA通道称做ZDMA(通用DMA),连接在SSB(系统总线)上,另外两个DMA通道称做 BDMA(桥DMA),连接于SSB和SPB(外设总线)之间的接口层。连接于SSB上的ZDMA控制器可以用于从存储器到存储器,从存储器到固定目标的 I/O存储器,和从I/O 设备到存储器之间的数据传输。另外的两个BDMA 控制器主要作用是在外部存储器和内部外设之间传输数据,这里的I内部外设包括SIO,IIS,TIMER和UART等。BDMA与ZDMA可以通过软件启动,也可以通过硬件启动。此设计中我们使用UART0,与其对应的DMA通道为BDMA0。其控制器框图如图1所示。

S3c44b0x的UART单元提供2个独立的异步串行I/O口,每个口均可以工作于中断模式或者DMA模式,即 UART可以产生内部中断请求或者DMA请求,在CPU的串行I/O口之间传送数据,支持高达115.2KBPS的传输速率,每个UART通道包含2个 16位的分别用于发送和接收的FIFO通道。

3、硬件电路设计

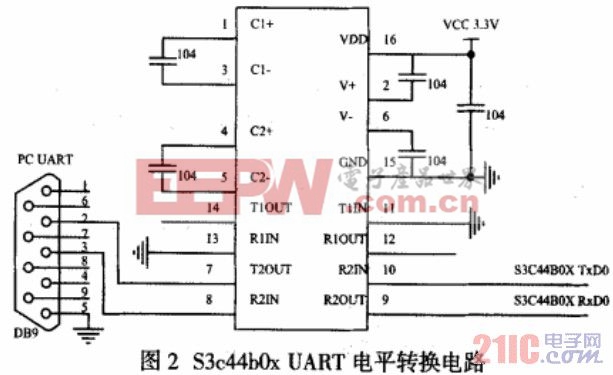

由于S3c44b0x自带支持UART的DMA控制器,所以关于DMA硬件部分不需要作任何的工作。S3C44B0X的I/O口电压为3.3V,而PC机一端的串口采用RS232电平,所以中间要经过电平转换,在此采用SP3232E芯片。连接电路如图2所示。

评论