Cortex-M3内核的异常处理机制及其新技术研究

引言

本文引用地址:http://www.amcfsurvey.com/article/170513.htmCortexM3是ARM公司第一款基于ARMv7M的微控制器内核,在指令执行、异常控制、时钟管理、跟踪调试和存储保护等方面相对于 ARM7有很大的区别。尤其在异常处理机制方面有很大的改进,其异常响应只需要12个时钟周期。NVIC(Nested Vectored Interrupt Controller,嵌套向量中断控制器)是CortexM3处理器的一个紧耦合部件,可以配置1~240个带有256个优先级、8级抢占优先权的物理中断,为处理器提供出色的异常处理能力[1].同时,抢占(preMemption)、尾链(tailMchaining)、迟到 (lateMarriving)技术的使用,大大缩短了异常事件的响应时间。

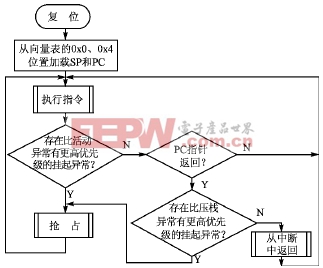

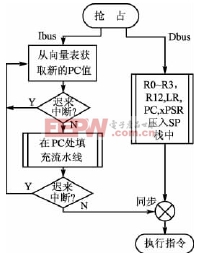

异常或者中断是处理器响应系统中突发事件的一种机制。当异常发生时,CortexM3通过硬件自动将编程计数器(PC)、编程状态寄存器(xPSR)、链接寄存器(LR)和R0~R3、R12等寄存器压进堆栈。在Dbus(数据总线)保存处理器状态的同时,处理器通过Ibus(指令总线)从一个可以重新定位的向量表中识别出异常向量,并获取ISR函数的地址,也就是保护现场与取异常向量是并行处理的。一旦压栈和取指令完成,中断服务程序或故障处理程序就开始执行。执行完ISR,硬件进行出栈操作,中断前的程序恢复正常执行。图1为CortexM3处理器的异常处理流程[2].

图1 CortexM3异常处理流程

1 CortexM3异常类型

同ARM7相比,CortexM3在异常的分类和优先级上有很大的差异,如表1所列。

表1CortexM3异常类型及优先级

CortexM3将异常分为复位、不可屏蔽中断、硬故障、存储管理、总线故障和应用故障、SVcall、调试监视异常、PendSV、 SysTick以及外部中断等。CortexM3采用向量表来确定异常的入口地址。与大多数其他ARM内核不同,CortexM3向量表中包含异常处理程序和ISR的地址,而不是指令。复位处理程序的初始堆栈指针和地址必须分别位于0x0和0x4.这些值在随后的复位中被加载到适当的CPU寄存器中。向量表偏移控制寄存器将向量表定位在CODE(Flash)或SRAM中。复位时,默认情况下为CODE模式,但可以重新定位。异常被接受后,处理器通过 Ibus查表获取地址,执行异常处理程序。

在CortexM3的优先级分配中,较低的优先级值具有较高的优先级。NVIC将异常的优先级分成两部分:抢占优先级(preMemption priority)部分和子优先级(subMpriority)部分,可以通过中断申请/复位控制寄存器来确定两个部分所占的比例。抢占优先级和子优先级共同作用确定了异常的优先级。抢占优先级用于决定是否发生抢占,一个异常只有在抢占优先级高于另一个异常的抢占优先级时才能发生抢占。当多个挂起异常具有相同的抢占优先级时,子优先级起作用[3].通过NVIC设置的优先级权限高于硬件默认优先级。当有多个异常具有相同的优先级时,则比较异常号的大小,异常号小的被优先激活。

2 CortexM3异常处理

2.1 异常的进入

当一个异常出现以后,CortexM3处理器由硬件通过Dbus保存处理器状态,同时通过Ibus读取向量表中的SP,更新PC和LR,执行中断服务子程序。

为了应对堆栈操作阶段到来后的更高优先级异常,CortexM3支持迟到和抢占机制,以便对各种可能事件做出确定性的响应。

抢占是一种对更高优先级异常的响应机制。CortexM3异常抢占的处理过程[2] 如图2所示。当新的更高优先级异常到来时,处理器打断当前的流程,执行更高优先级的异常操作,这样就发生了异常嵌套。迟到是处理器用来加速抢占的一种机制。如果一个具有更高优先级的异常在上一个异常执行压栈期间到达,则处理器保存状态的操作继续执行,因为被保存的状态对于两个异常都是一样的。但是,NVIC马上获取的是更高优先级的异常向量地址。这样在处理器状态保存完成后,开始执行高优先级异常的ISR.

图2 异常抢占流程

评论