基于AT89S52单片机的多功能电子万年历

引言

本文引用地址:http://www.amcfsurvey.com/article/170491.htm随着生活节奏的日益加快,人们的时间观也越来越重,同时对电子钟表、日历的需求也随之提高。因此,研究实用电子时钟及其扩展应用,有着非常现实的意义,具有很大的实用价值。

本系统程序由主程序、中断服务函数和多个子函数构成。主函数主要完成各子函数和中断函数的初始化。定时中断函数主要完成时钟芯片的定时扫描及键盘扫描。时钟芯片的读写函数主要是将时间、日历信息读出来,并把要修改具体值写入时钟芯片内部。

系统的硬件设计与电路原理

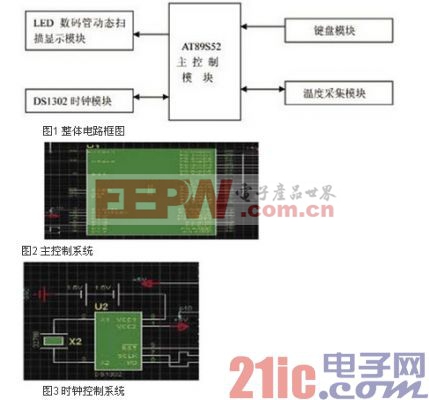

电路设计框图

系统硬件概述

本电路是由AT89S52单片机为控制核心,具有在线编程功能、低功耗、能在3V的超低压工作。时钟电路由DS1302提供,它是一种高性能、低功耗、带RAM的实时时钟电路,它可以对年、月、日、周日、时、分、秒进行计时,工作电压为2.5V~5.5V。采用三线接口与CPU进行同步通信,并可采用突发方式一次传送多个字节的时钟信号或RAM数据。DS1302内部有一个31×8的用于临时性存放数据的RAM寄存器。可产生年、月、日、周日、时、分、秒,具有使用寿命长、精度高和低功耗等特点,同时具有掉电自动保存功能。

主控制模块

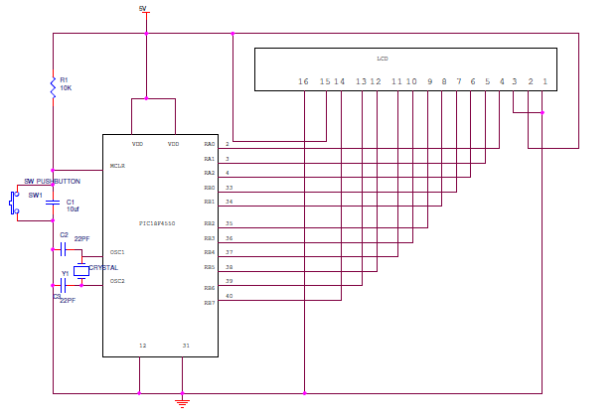

单片机主控制模块的设计

AT89S52单片机为40引脚双列直插芯片,有四个I/O口P0,P1,P2,P3,MCS-51单片机共有4个8位的I/O口(P0、P1、P2、P3),每一条I/O线都能独立地作输出或输入。

时钟电路模块

时钟电路模块的设计

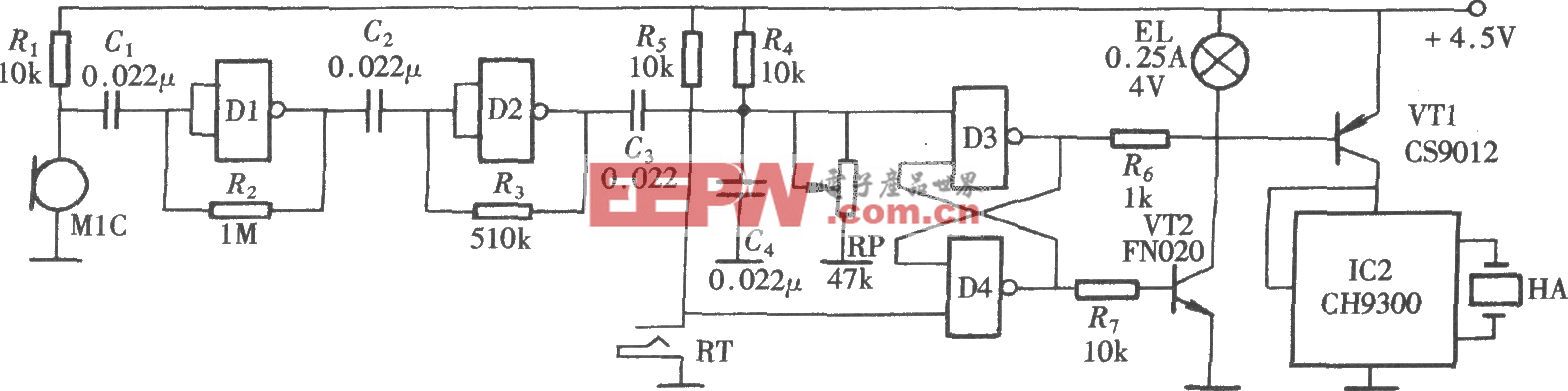

DS1302的引脚排列如图3所示,其中Vcc1为后备电源,Vcc2为主电源。在主电源关闭的情况下,也能保持时钟的连续运行。DS1302由Vcc1或Vcc2两者中的较大者供电。当Vcc2大于Vcc1+0.2V时,Vcc2给DS1302供电;当Vcc2小于Vcc1时,DS1302由Vcc1供电。X1和X2是振荡源,外接32.768KHz晶振。RST是复位/片选线,通过把RST输入驱动置高电平来启动所有的数据传送。RST输入有两种功能:首先,RST接通控制逻辑,允许地址/命令序列送入移位寄存器;其次,RST提供终止单字节或多字节数据的传送手段。

时钟电路模块工作原理

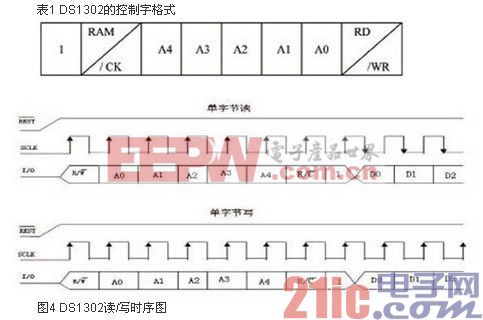

DS1302在每次进行读、写程序前都必须初始化,先把SCLK端置“0”,接着把RST端置“1”,最后才给予SCLK脉冲;读/写时序如图4所示。表1为DS1302的控制字,此控制字的位7必须置1,若为0则不能对DS1302进行读写数据。对于位6,若对程序进行读/写时RAM=1,对时间进行读/写时,CK=0。位1至位5指操作单元的地址。位0是读/写操作位,进行读操作时,该位为1;该位为0则表示进行的是写操作。控制字节总是从最低位开始输入/输出的。表2为DS1302的日历、时间寄存器内容:“CH”是时钟暂停标志位,当该位为1时,时钟振荡器停止,DS1302处于低功耗状态;当该位为0时,时钟开始运行。“WP”是写保护位,在任何的对时钟和RAM的写操作之前,WP必须为0。当“WP”为1时,写保护位防止对任一寄存器的写操作。

DS1302的控制字节

DS1302的控制字如表1所示。控制字节的高有效位(位7)必须是逻辑1,如果它为0,则不能把数据写入DS1302中,位6如果为0,则表示存取日历时钟数据,为1表示存取RAM数据;位5至位1指示操作单元的地址;最低有效位(位0)如为0表示要进行写操作,为1表示进行读操作,控制字节总是从最低位开始输出。

数据输入输出(I/O)

在控制指令字输入后的下一个SCLK时钟的上升沿时,数据被写入DS1302,数据输入从低位即位0开始。同样,在紧跟8位的控制指令字后的下一个SCLK脉冲的下降沿读出DS1302的数据,读出数据时从低位0位到高位7。如图4所示。

评论