一种基于DDR高速图像缓存的实现

随着半导体传感器技术的发展,在实际应用中越来越多地用到了高帧频、大面阵的CCD相机以获取高质量、高分辨率的图像数据。以分辨率为1K×1K、帧频为200f/s、8bit灰度级的相机为例,其图像数据流速率就将高达200MB/s,这对图像的高速缓存和记录提出了挑战。高速缓存的实现是实时记录的前提条件,高速图像记录之前必须采用合理的缓存机制来完成高速图像数据缓存。

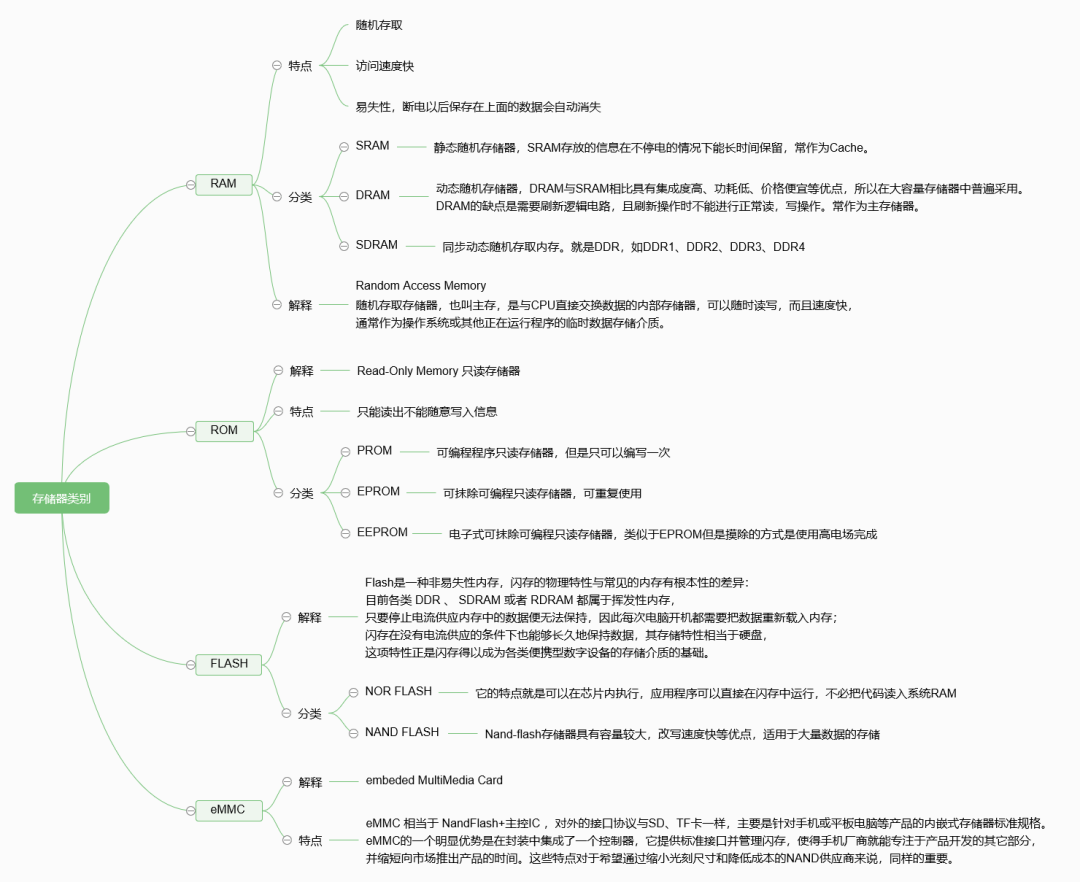

目前高速缓存实现方案有三种: 第一种是FIFO(先进先出)方式,FIFO存储器就像数据管道一样,数据从管道的一端流入,从另一端流出,先进先出,省略了地址线,接口简单方便,其缺点是容量可扩展性差。第二种是双口RAM方式,具有两套独立的数据、地址和控制总线,因而可从两个端口同时读写而互不干扰,能达到很高的传输速度,并且具有随机存取的优点,缺点是需要用户产生地址逻辑。 第三种是高速SRAM切换方式,高速SRAM只有一套数据、地址和控制总线,可通过三态缓冲门来实现两块SRAM的乒乓切换操作,该方案提高了系统带宽,缺点是切换电路控制比较复杂。

目前高速缓存方案中常采用三种介质:第一种是SRAM,其具有操作简单的特点,但是昂贵的价格和容量的有限性限制了其在高速大容量的缓存中的应用。第二种是SDRAM,由于需要进行刷新、预充电等操作,控制难度大于SRAM,同时由于其数据传输只在时钟沿上沿进行,因此其传输带宽还是受时钟频率的限制。第三种是DDR SDRAM,克服了SDRAM数据带宽的问题,在时钟的上下沿均传输数据,带宽是SDRAM的两倍,性价比高,是目前高速缓存的最理想介质。

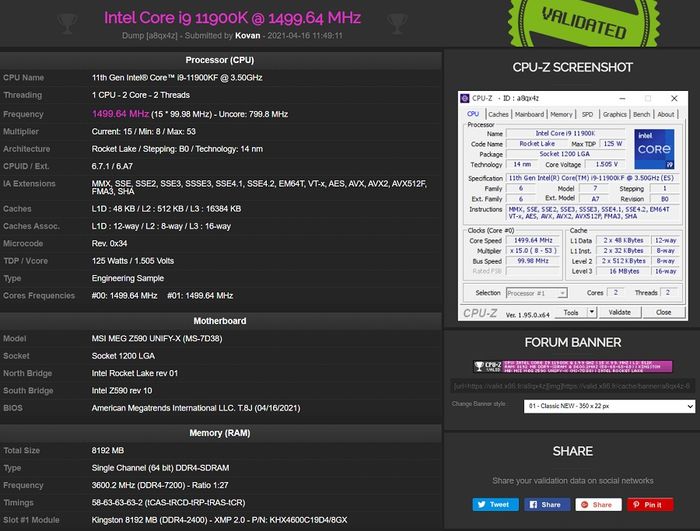

本文以Micron DDR SDRAM[1]作为缓存介质,发挥了FIFO接口简单、DDR的容量可扩展性和高数据带宽的优点。在工作时钟100MHz的条件下,以FIFO作为缓存方案实现了缓存容量32MB、数据传输率高达360MB/s的高速图像缓存,弥补了FIFO容量小和DDR用户接口逻辑复杂的缺点,具有较好的应用前景。

1 系统设计

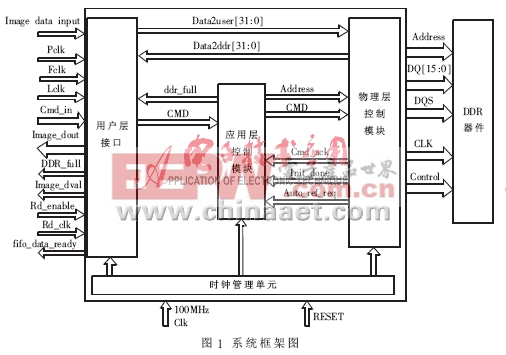

为提高设计的可移植性和可扩展性,采用了模块设计的方法,设计四个模块来完成图像缓存功能。系统框架如图1所示。用户层接口模块负责与用户进行通信,接收用户命令和图像数据并产生控制命令到应用层控制模块;应用层控制模块负责接收来自用户层命令以及物理层控制模块的状态反馈信号,产生读写命令及DDR操作地址发送到物理控制模块;物理层控制模块负责接收应用层发送来的操作地址和命令以及和用户层进行数据通信,同时负责产生DDR器件操作所需要的时序逻辑功能来完成对DDR器件的物理层操作。

1.1 物理层控制模块

DDR器件在上电过程中有一系列复杂的操作:上电后至少等候200?滋s然后连续执行如下一连串命令:

全充电→空命令→配置外部模式寄存器→空命令→配置内部模式寄存器→全充电→空命令→自动刷新→空命令→自动刷新→空命令→用户发出任何有效操作命令。

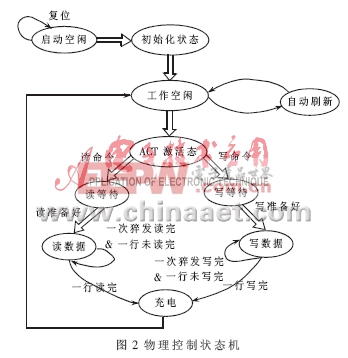

该模块的状态机如图2所示,复位或者上电后进入初始化状态,初始化完成后进入工作等待(空闲)中,由于DDR器件的构造特点,需要每隔64ms对器件所有存储单元进行一次刷新。DDR器件本身具有自动刷新计数器,刷新一行计数器便增加一,因此自动刷新的时间间隔由DDR的行数决定,本设计采用Micron MT46V32M16器件,行数为8K,计算得到相邻自动刷新命令的间隔为7.8μs。设计中采用一个计数器,每隔7.8?滋s就发出一个自动刷新的命令,控制器在工作空闲状态下响应并发出自动刷新命令。

评论