数字放大器的单端设计

数字放大器最大优点之一是其具备设计复用的数字数据通路的灵活性。因为信号在到达扬声器之前是保持在数字域的,所以在信号路由方面具有更大的灵活性。这种灵活性同时也能处理开发过程中和生产过程的填料选择和/或固件变更。数字放大器有一个被称为单端工作的常规模式。本文描述了单端设计基础和工程相关的权衡考虑。

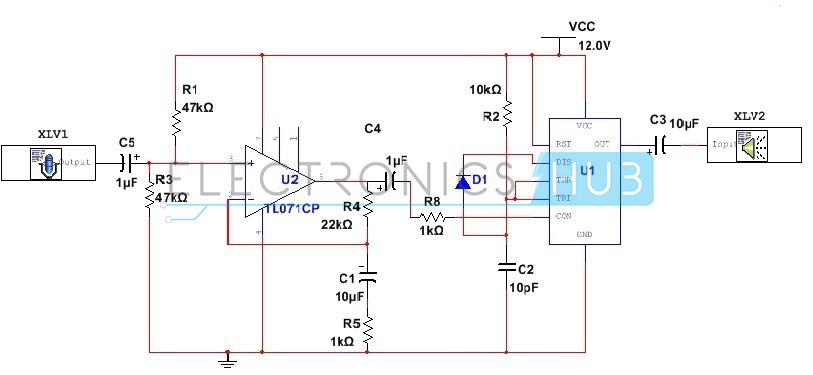

通常,数字放大器具有两级架构。如图1所示,脉冲宽度调制(PWM)处理器后紧随着功率级。逻辑级的PWM处理器通常接收IIS格式的音频数据。它执行音频处理并将脉冲编码调制(PCM)数据转换成PWM数据。一般情况下,通过I

包含MOSFET H桥的功率级如图1所示。这里是将MOSFET用作开关,使得+V电压能通过正/负向跨接到扬声器。对于将扬声器连接在两个MOSFET半桥之间的大多数立体声功率级而言,桥接负载(BTL)是标准的配置。单端(SE)是指每个扬声器由单个MOSFET半桥驱动。相对BTL而言,SE的通道总数是其两倍;但对于特定的输出负载,SE各通道的功率约为其25%。在SE模式中,当PWM信号为高电平时,接到扬声器上的+V电压是正向的;而PWM信号为低电平时,表示扬声器接地。

数字放大器的单端工作模式如图2所示,这与线性音频放大器的单端工作并无太大差别。主要的区别在于重建滤波器(二阶LC滤波器)把PWM信号中的高频成分滤出,而只保留基带音频信号。直接将音频信号供至扬声器将导致一个很大的直流电压加在扬声器上,其值等于PVDD/2。由于扬声器阻抗具有很大的感抗成分,这相当于在电感两端加载了一个很大的DC电压,会导致电流直线上升至非常大值,进而可能损坏扬声器。因此,在放大器与扬声器之间放置一个大电容以滤掉DC成分。但是,该电容也会使较低音频成分产生衰减并在约为1/(2πRspC)时出现3dB点,其中Rsp是扬声器的阻抗。为了使更多的频率带宽通过扬声器,须使用更大电容值的电容,但这要以成本和PCB面积为代价。

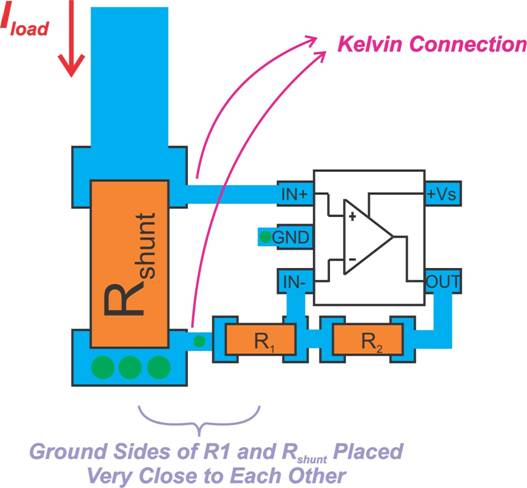

在上述的单端配置中,音频信号以地为参考点。换言之,扬声器的一端是接地的。隔离DC的另一方法是使用分离电容(split-cap)配置(如图3所示),因此音频信号此时的参考电压是PVDD/2。从交流(AC)的角度来说,当Csm=Cb/2时,图2和图3就没有区别。额外插入电容时,Cs的半额定电流是Cb的一半,且Cs的等效串联电阻(ESR)是Cb的两倍,而音频或温度性能无任何变化。

图1:具有H桥功率级的数字放大器数据通路

图2:带直流隔离电容配置的单端数字放大器

图3:带分离电容配置的单端数字放大器

与隔离电容配置相比较,分离模式配置的最大优点是增加了电源纹波抑制比(PSRR)。图4所示的曲线为TI的TAS5086/5142评估模块(EVM)的PSRR测量值。在该EVM中,TAS5142评估板的功率级被配置成单端模式。也许有人会对一个开环单端放大器能具有如此高的PSRR感到奇怪。事实的原因是,PVDD的电压变化(ΔPVDD)都处于分离电容的中点(都为ΔPVDD/2),从而使得经过扬声器的PVDD变化被抵消掉了。

图4:TI TAS5086/5142 EVM的单端PSRR曲线

SE分离模式的配置还需要解决下面两个设计问题。如前所述,经过重建滤波后的音频信号有一个大小为PVDD/2的DC成分。若电容Cs是理想的,则两电容的电压都可充至PVDD/2,且没有DC成分流经扬声器。然而,由于两个电容不是理想的且存在偏差,所以直流电压值并不等于PVDD/2。因此,上电后当音频信号传至扬声器时,将会有一个DC电压通过扬声器,从而导致“劈啪”声。由于分离电容的充电时间为RC所决定的时间常数所限定,所以会导致另一个相关的问题。虽然,在分离电容充完电之前只要MOSFET不产生开关动作,该问题便不会发生。但实际应用中这一点却很难实现,因此会产生很大的“劈啪”声。

针对上述两个问题的解决方案是带有一个专用于实现快速充电到PVDD/2的半桥的功率级,这在TAS

实际应用中,包括上电“劈啪”声、SNR、PSRR、总谐波失真+噪声(THD+N)在内的单端放大器的音频性能数据是相当好的,只比BTL的音频性能稍为逊色。

评论