基于ID200的数字广播接收机DF50C系统设计

随着数字广播DAB的发展,目前全球已有1000多个DAB/DMB台开播,包括中国北京、上海、广东等地,但DAB/DMB解码核心芯片仍是瓶颈,接收终端开发严重滞后。ID200是西安西芯微电子公司近年来在国内开发的DAB/DMB基带解码核心芯片,其集成度、功耗、性能、价格指标均处于国际领水平,基于此芯片及核心技术,不仅可以简化DAB数字音频广播接收机的设计,同时可以降低DAB数字音频广播接收机的成本,进而提高其市场竞争力。

DAB基带芯片ID200简介

ID200是一款面积小、功耗低、可用于移动和便携设备的DAB解码器(DAB基带解码器和MPEG L2音频解码器)芯片。该芯片可以对DAB传输帧进行1.5Mbps全速解码,包括数字混频、同步/跟踪和解调。基带解码器可同时对传输帧内的两路音频、数据或视频节目进行解码。解码后的音频节目可以通过片内MPEG L2音频解码器播放,而数据/视频节目可以通过片外CPU进一步处理和显示。芯片上集成了1Mb SRAM。

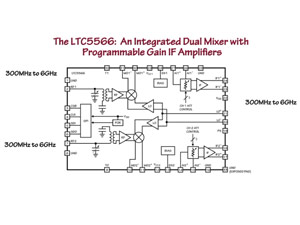

ID200 DAB基带解码器架构如图1所示。DAB基带解码的功能可以简单概括为:系统首先将模拟的DAB 中频信号通过ADC转换成数字中频信号,然后利用数字的方法进行IQ分量的分离和滤波从而得到复数形式的OFDM时域信号,接下来利用FFT得到各个副载波的样点并完成频率解交织,然后利用FFT计算的结果进行DQPSK解调并完成时间解交织,最后用Viterbi解码器进行信道解码,从而恢复出DAB节目源数据。节目源(MPEG音频数据流)再经过音频解码器播放,得到高质量的声音。

图1: DAB基带解码器结构示意图。

DF50C的硬件结构

DAB接收机DF50C的构成需要ID200芯片 + RF 芯片, 以及ADC 和音频DAC(驱动耳机)。FM 接收机采用单芯片方案。DAB 接收和FM 接收共享同一根天线。DAB+FM模块需要一个MCU 芯片来控制RF芯片、ID200 、音频DAC、FM 芯片。接收机生产厂家亦可通过此MCU 芯片实现独特的界面设计及功能扩充。基带解码不需要外加SRAM。

DF50C的硬件结构见图2。接收机各部分的功能分别为:

◆ RF芯片采用的是MAX2170,RF模块完成调谐的功能,同时将射频DAB信号从Band Ⅲ(174~230 MHz)或者L Band(1452~1492 MHz)搬移到中频(2.048MHz或38.912MHz)。根据DAB协议,RF模块必须具备能够接收这两个频段信号的能力;

◆ A/D模块实现将RF输出的基带模拟信号转换为数字信号,从而方便后面的DAB数字解码的实现;

◆ 基带解码模块是DAB接收机最核心的部分。完成DAB信道解码和OFDM解调、DQPSK解调等工作。通过基带解码处理后的数据包括声音广播和数据业务。声音广播业务可以继续进行声音解码,数据业务要送入相应的解码单元进行具体的业务解码。

◆ MCU采用了Microchip的P18f45j10,MCU控制模块,用来管理整个系统中各个模块的配置,以及控制各个模块的工作和码流。同时它也提供人机交互的功能,如响应键盘信息,控制LCD显示信息。它提供了SPI、I2C等总线接口,方便与外部各模块的通信。

图2中虚线框内即为DAB接收机的基带解码和信源解码部分。

图2: DAB接收机原理框图。

DF50C的主要技术指标

DAB 接收性能:

◆ 数字广播标准 DAB ETSI 300 401

◆ 我国DAB 国家标准GY/T214.2006

◆ L 波段和3 波段的高速移动接收

◆ 灵敏度: -97dBm/3 波段, -97dBm/L 波段

◆ 可实现DAB 模式 1, 2, 4 的自动识别和接收

◆ MPEG L2 音源解码,支持48KHz, 24KHz 采样频率,自动识别声道模式,支持单通道、双通道、立体声;

◆ LCD 显示屏, 显示DAB 节目台名,动态文字,节目类型,DAB 信号强度和BER

◆ 时间显示,包括 年,月,日,小时,分

◆ 提供功能扩展的JTAG USB 界面

◆ 低功耗的DAB分时工作模式

◆ 模块功耗:140mW@128Kpbs DAB 接收

◆ DAB+FM 接收机样机典型功耗:240mW

◆ 电源: 3.0V / 1.8V

◆ DAB+FM 模块尺寸:35 x 65 x 3 mm2

◆ DAB+FM 模块PCB 设计: 仅用2 层金属

FM 接收性能:

◆ 自动搜索模式和手动搜索模式

◆ FM 电台频率显示

◆ RSSI 信号强度显示

◆ 支持RDS 数据和文字解码

◆ FM IC 功耗:54mW @ FM接收

DF50C软件设计

FIC解码实现

FIC是DAB传输帧中的快速信息信道,FIC没有经过时间交织,因此它被称为快速信息信道,由于它提供了各子信道和业务的索引,因此也是接收机必须首先处理的部分。同时,FIC不是一成不变的,因此对FIC的解码要周期性的进行,以保证接收机及时针对FIC的变化做出相应的反应。通过FIC解码流程图3,FIC解码后可以清楚地得到每个业务成分的详细信息,MCU中的MMI程序可以根据这些索引信息控制基带,选择自己喜欢的节目。

图3: FIC解码流程图。

MMI软件设计

DF50C MMI软件设计可以分为两大部分,如图4所示,一部分是由FIC解码模块构成的子信道及业务信息解码模块和动态文字解码模块,另一部分为人机接口模块,包括人机接口菜单控制模块、基带寄存器设置模块、音频控制模块、FLASH存储模块、键盘输入模块、LCD显示控制模块、RF控制模块等。解码模块将各种节目相关信息解出后交由人机接口模块根据用户的需要来管理和调用。之所以将解码模块与人机接口模块分开是因为解码模块与硬件联系较少,而其它模块中大都包含硬件接口驱动程序,同时也考虑到人机接口菜单设计结构上的灵活性,将解码模块独立出来,既利于程序在不同硬件上的移植,也使其在人机接口菜单结构改变的情况下仍能被复用。

图4:MMI软件设计。

DF50C系统测试

图5是基于ID200的DAB接收机DF50C系统。DF50C能正确接收Band Ⅲ(174~230 MHz)和L Band(1452~1492 MHz)中每个频点的DAB信号,并且灵敏度均能达到-97db。可实现在高速移动中对L波段和Ⅲ波段的稳定接收。对比特率为128kbps DAB音频数据流解码时,核心模块(包括RF芯片、AD芯片、基带芯片和MCU)部分的功耗为130mW。

图5: DAB接收机DF50C板卡。

DF50C系统集成了FM芯片、时钟芯片、flash芯片和红外芯片,完成了DAB、FM的人工和自动频率搜索,定时开关机,节目收藏以及红外遥控等功能。DF50C各项技术指标达到设计要求,实现了低成本,低功耗,多功能的DAB接收机设计。该产品的面世填补了中国DAB核心芯片和整机技术的空白,推动DAB在中国的发展。

评论