基于NiosII的 低码率实时H.264视频编码器

H.264标准作为新一代视频编码标准,是面向多比特率的视频编码标准,也称JVT/AVC标准,既可用于高码率的HDTV和数字存储系统,也可用于低码率的实时通信系统。在相同的图像质量情况下,H.264比H.263和MPEG一4可以节省20%~50%的码率。就其基本档次而言,编码器的复杂度是H.263的10倍左右。H.264良好的网络亲和性和优异的压缩性能使其成为视频应用的首选,但其巨大的运算量成为许多应用的瓶颈。笔者基于NiosII设计了一种低码率实时应用的编码系统。该系统充分利用FPGA的并行设计结构,对视频数据采用高压缩比的H.264标准编码,能很好地满足低码率实时编码的要求。

1 H.264编码系统结构设计

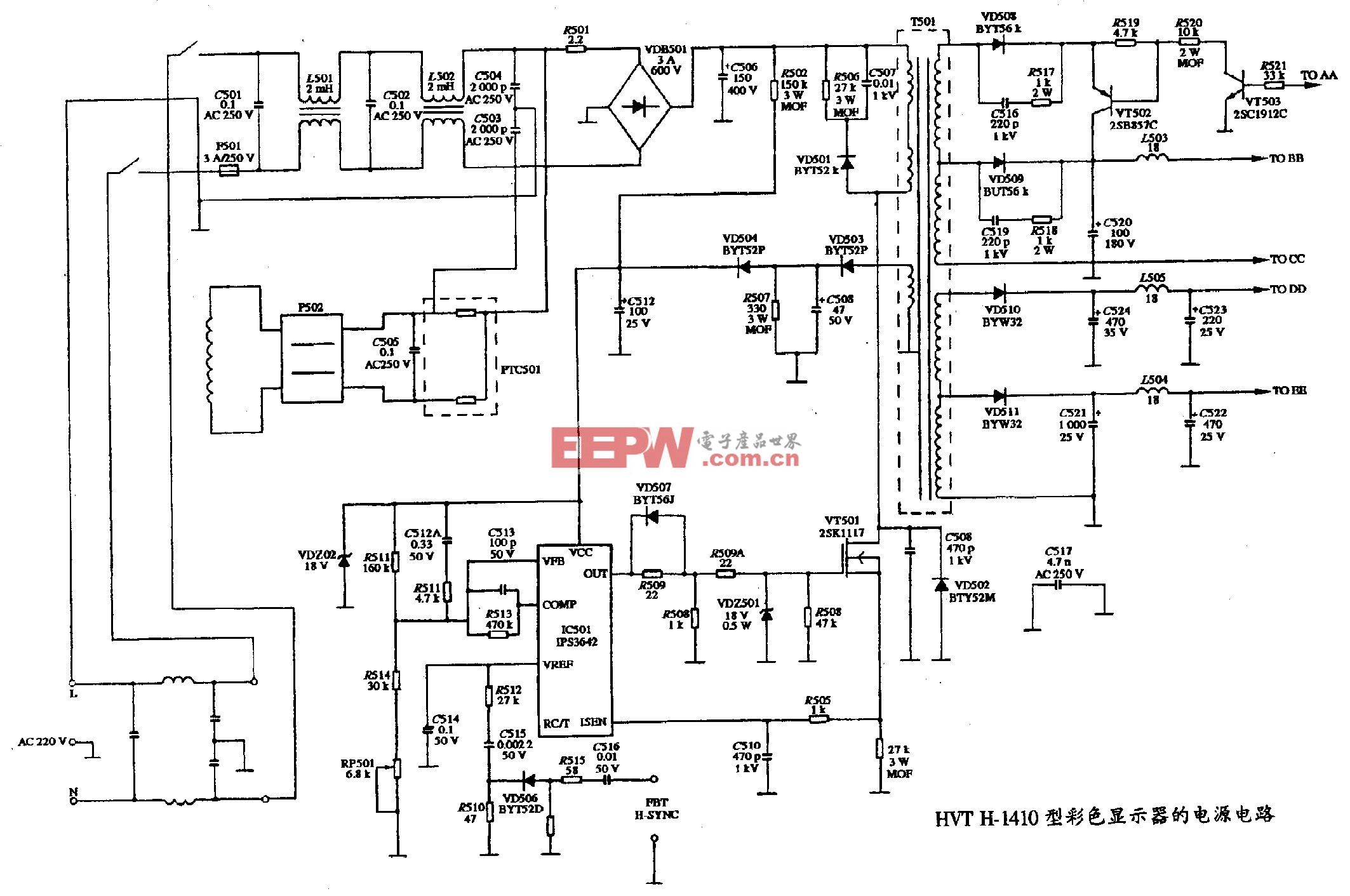

根据H.264/AVC编码器原理及结构,同时考虑到现有硬件资源的限制以及该设计的应用需求,设计了图1所示的H.264/AVC编码系统结构。

摄像头摄入的视频图像首先经过视频采集模块处理,并将当前帧的图像数据存入SRAM。然后,以宏块MB(macroblock)为单元,从SRAM中读取原始图像,并根据MB所在图像帧内的位置,读取重建帧中的参考像素进行帧内预测,并将预测宏块与当前宏块像素做差即可得到预测残差。接下来,对残差图像进行整数DCT变换或Had―amard变换,并对变换输出进行量化。量化输出的残差图像一方面通过反变换和反量化处理生成重建图像供帧内预测作为参考,另一方面经过重排序、熵编码处理得到最终的图像压缩码流输出。

根据H.264/AVC标准,将所设计的整个编码系统从结构上划分为图像采集、帧内预测、变换量化、熵编码等几个主要部分。各个模块之间通过流水线的方式进行处理,可以有效地提高硬件的执行效率。

2 基于Cyclone II FPGA的H.264编码器的实现

系统采用SOPC的设计方式,主要由视频采集模块、NiosII处理器系统组成。采用Altera公司的DE2开发板为开发平台,将视频采集、NiosII处理器集成到一个SOPC系统中。其中NiosII处理器系统要承担图像采集控制、图像的H.264压缩编码工作。为了保证实时性,在充分分析H.264软件算法运行时间后,采用自定义模块对H.264编码器关键算法进行硬件加速。

2.1 视频采集模块

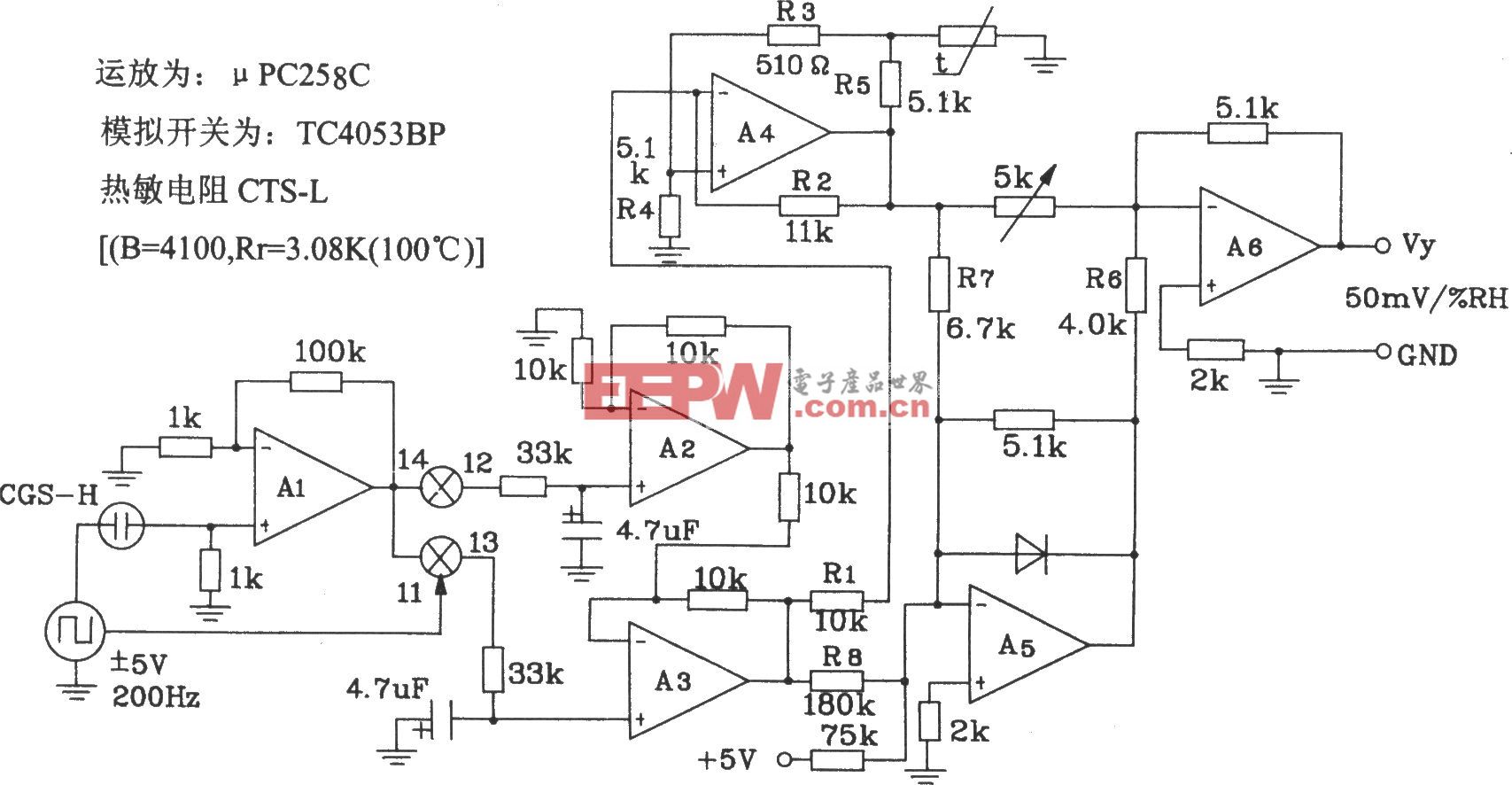

视频采集是视频图像处理、传输的前提,采集到的数字视频图像好坏将直接影响到视频处理的结果。图2给出了图像处理系统的视频采集结构。

ADI公司的多制式视频解码芯片ADV7181B对采集的视频图像进行模数转换。ADV7181B可以自动检测诸如NTSC、PAL和SEC0M制式的基带视频信号,并将其转换为基于4:2:2取样的16/8位兼容的CCIR601/CCIR656格式的数字视频信号;具有6路模拟视频输入端口,且采用单一的27 MHz晶振时钟输入;用户可以通过两线的I2C接口对ADV7181B的工作模式进行配置。

系统上电时,首先使用I2C模块对ADV7181B的内部寄存器进行配置。由于摄像头输出的是PAL制式的模拟视频信号,因此需要相应地将ADV7181B配置为PAL制式的模拟视频信号输入,并将其转换为CCIR656格式的数字视频信号。ADV7181B将转换得到的实时数字视频图像的亮度信号、色度信号(TD_DAT)以及行、场同步信号(TD_HS/VS)同时输入到FPGA芯片中,通过图像采集模块提取需要的数字图像信息,并将其转存至AlteraDE2开发板提供的具有512 KB存储容量的SRAM中,用于缓存待处理图像帧。

下面介绍图像采集模块的设计与实现方法。

根据上面对视频采集部分硬件结构的分析,设计了图3所示的视频采集模块结构框图。可以看出,图像采集模块主要包含图像提取、色度取样率变换、Y/Cb/Cr图像分量分离以及图像缓存SRAM读写控制等单元。

评论