基于TMS320VC5402的音频信号采集与处理系统

近年来,随着DSP技术的普及和低何等、高性能DSP芯片的出现,DSP已越来越多地被广大的工程师所接受,并越来越广泛地被应用于各个领域,例如:语音处理、图像处理、模式识别及工业控制等,并且已日益显示出其巨大的优越性。DSP是利用专门或通用的数字信号处理芯片,以数字计算的方法对信号进行处理,具有处理速度快、灵活、精确、抗干扰能力强、体积小及可靠性高等优点,满足了对信号快速、精确、实时处理及控制的要求。基于TMS320C5402芯片,笔者研制了一套音频信号实时采集与处理系统,并已作为有关音效器研制的硬件试验平台。

本文引用地址:http://www.amcfsurvey.com/article/167072.htm1 系统总线方案

系统总线方案框图如图1所示。音频信号(如:电吉它的单声道声音信号是150mV的电信号)经过高精度高速的ADC转换后得到一串数字信号,分帧输入到波形输入缓冲区RAM。然后由手动控制一种或几种处理算法将音频信号调入TMS320C5402的内部进行高速运算。经过处理的音频信号,再输入到高精度高速的DAC转换器中,还原成模拟的声音信号,经音箱功率放大电路放大输出。

利用缓冲区的目的是进行音效的实时处理。系统中各模块是同时进行处理的,一部分信号正在ADC中进行转换,而另一部分信号则在DSP处理器中同时进行算法处理,即整个系统是以流水线的方式进行工作。

2 硬件电路的设计

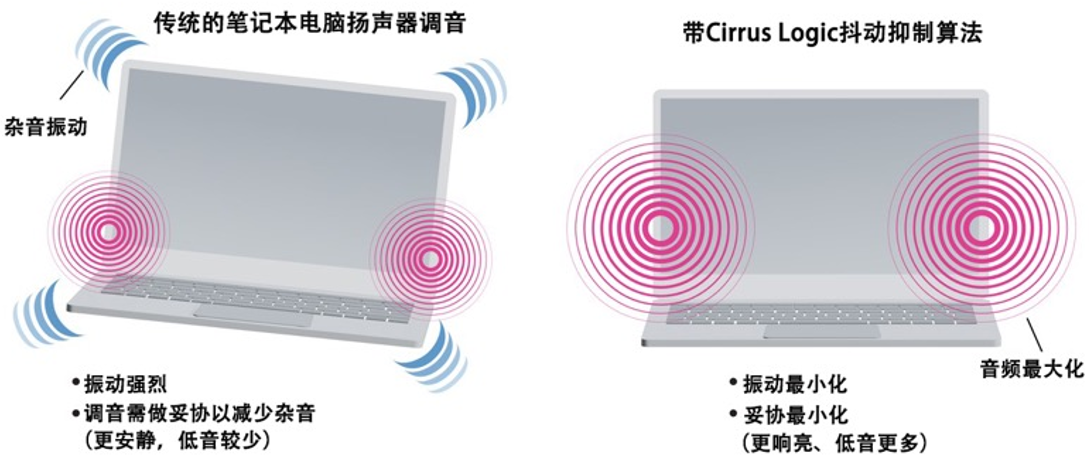

高保真的音频系统应该具有较宽的动态范围,选择16~24位的ADC和DAC能完全捕获或恢复高保真的音频信号。系统的核心芯片(DSP)选用美国TI公司的TMS320VC5402[1](以下简称'C5402)。

2.1 DSP芯片

作为DSP家庭高性价比代表的16位定点DSP芯片,'C5402适用于语音通信等实时嵌入应用场合。与其它'C54X芯片一样,'C5402具有高度灵活的可操作性和高速的处理能力。其性能特点如下:操作速率可达100MIPS;具有先进的多总线结构,三条16位数据存储器总线和一条程序存储器总线;40位算术逻辑单元(ALU),包括一个40位桶形移位器和两个40位累加器;一个17×17乘法器和一个40位专用加法器,允许16位带/不带符号的乘法;整合维特比加速器,用于提高维特比编译码的速度;单周期正规化及指数译码;8个辅助寄存器及一个软件栈,允许使用业界最先进的定点DSP C语言编译器;数据/程序寻址空间为1M×16bit,内置4K×16bit ROM和16K×16bit RAM;内置可编程等待状态发生器、锁相环(PLL)时钟产生器、两个多通道缓冲串口、一个与外部处理器通信的8位并行HPI口、两个16位定时器以及6通道DMA控制器且低功耗。与'C54X系列的其它芯片相比,'5402具有高性能、低功耗和低价格等特点。它采用6级流水线,且当RPT(重复指令)时,一些多周期的指令就变成了单周期的指令;芯片内部RAM和ROM可根据PMST寄存器中的OVLY和DROM位灵活设置。这些都有利于算法的优化。

'C5402采用3.3V和1.8V电源供电,其中I/O采用3.3V电源供电,芯片的核采用1.8V电源供电。而实际常用的只有5V电源,所以必须采用电源转换芯片。选用TPS7301和TPS7333两块电源转换芯片(它们都是TI公司为配合DSP而设计的电源转换芯片),分别接上适当的外围电阻,构成电阻分压器,即可调整两块芯片的输出电压分别为3.3V和1.8V。

PCM1800是双声道单片Δ-∑型20位ADC,单+5V电源供电,信噪比为95dB,动态范围为95dB,其内部嵌有高通滤波器,具有PCM音频接口和四种数据格式,分为主控和受控两种模式,采样频率可选为32kHz、44.4kHz和48kHz。

PCM1800构成音频信号采集系统时,主要涉及到BCK(位时钟信号)、LRCK(采样时钟信号)、FSYNC(帧同步信号)、DOUT(数字信号输出)、SYSCLK(系统时钟输入)这几个对时序有要求引脚。通过对引脚MODE0和MODE1进行编程,可让PCM1800工作于主控模式(Master Mode)。此时,BCK、LRCK、FSYNC均作为输出,其时序由PCM1800内部的时钟产生电路控制。但SYSCLK只能由外部提供(这里用'C5402的TOUT脚输出信号提供)。PCM1800的系统时钟只能是256fs、384fs或者512fs,这里fs是单频信号采样频率。在主控模式时,FSYNC用来指明PCM1800的DOUT输出的有效数据,它的上升沿表明一帧数据的起始,下降沿表明一帧数据的结束。FSYNC的频率是采样时钟频率LRCK的2倍 。在此模式下,位时钟信号BCK的频率是采样时钟频率LRCK的64倍。

通过对PCM1800的FMT0、FMT1两引脚编程(FMT0=1,FMT1=0),可以设置PCM1800输出的数据格式为20位的IIS格式。为了保证在数据处理时不影响新数据的接收以及在接收数据时不断正在进行的数据处理过程,采用了多通道缓冲同步串口(McBSP)。PCM1800与'C5402连接后,'C5402使用缓冲串口0接收数据,各种同步信号由PCM1800产生,'C5402是被动接收各种信息。PCM1800与'C5402的硬件接线图如图2所示。

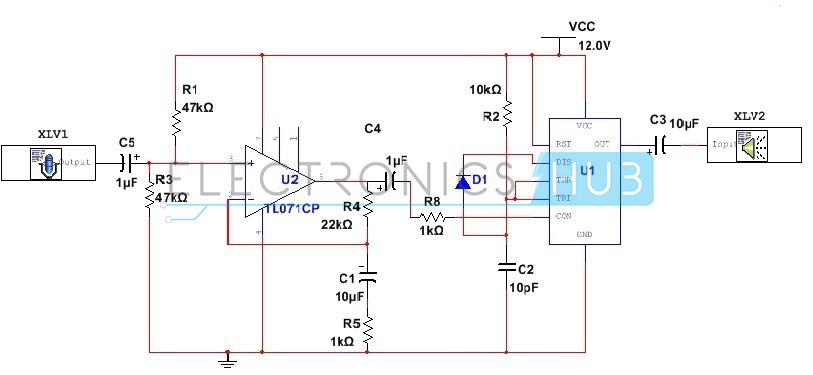

2.3 D/A电路

PCM1744是双声道立体声DAC,包含数字滤波器和输出放大器,动态范围为95dB,具有多种采样频率可选,最高可达96kHz。采用24位的IIS数据输入格式。PCM1744的操作主要涉及到LRCIN(采样时钟信号输入)、BCKIN(位时钟信号输入)、SCKI(系统时钟输入)、DIN(数据输入)这几个对时序有要求的引脚。PCM1744与'C5402连接后,'5402使用缓冲串口1发送数据,各种时钟信号均由'C5402产生,PCM1744被动接收各种信息。PCM1744的系统时钟信号(SCKI)由'C5402的TOUT引脚提供,TOUT是'C5402的定时器输出信号引脚,有较强的驱动能力,可以驱动多个芯片。PCM1744的数据接收时钟格式必须是IIS格式,'C5402在缓冲串口寄存器中设置各种时钟方式时,必须满足IIS格式的要求。'C5402作为主动工作器件,可以对其缓冲串口输出信号进行调整。输出的采样时钟信号、位时钟信号可以在McBSP寄存器SRGR1和SRGR2中设置,设置遵循图3的原则。

评论