在视频监控系统中使用FPGA进行视频处理

视频监控系统是火车站、机场、银行、娱乐场所、购物中心甚至家庭保安的重要组件。随着安全风险的增加,对视觉监视和记录事件的需求以多种使用模式激增。因此,新架构必须为横跨一整套日渐繁杂的视频监控系统要求的成本效益方案提供可扩展性。

本文引用地址:http://www.amcfsurvey.com/article/166633.htm

上市时间的压力、新CODEC标准、日益广泛的要求(包括先进的目标探测、运动探测、目标跟踪和目标跟踪特性),这些不过是新型视频监控架构所面临挑战中的几项。伴随挑战而来的是对可扩展为不同性能范围的实现的需求。

视频监控和DVR系统

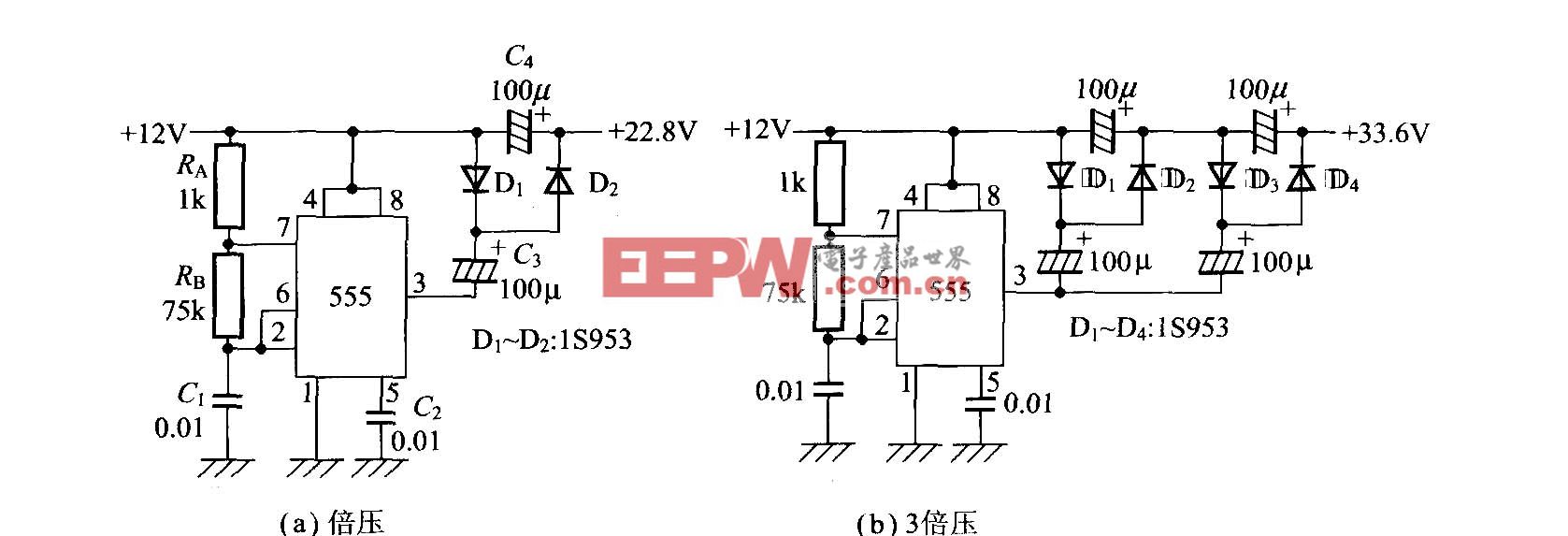

数字监控系统中的数字视频录像机(DVR)正在迅速采用先进的数字视频压缩。大多数DVR制造商从MPEG-4向H.264高清晰度(HD)CODEC转移,对更高分辨率和压缩速度的需求也随之增加。专用芯片(ASSP) 对大批量应用很有用,但缺少灵活性,开发成本高,而且开发时间较长;大多数高级数字媒体处理器则只能执行 H.264 HD 解码(而 H.264 HD 编码比解码还要复杂得多)。满足 H.264 HD 性能要求的最佳解决方案是使用一个 FPGA 加上一个外部 DSP 或数字媒体处理器。

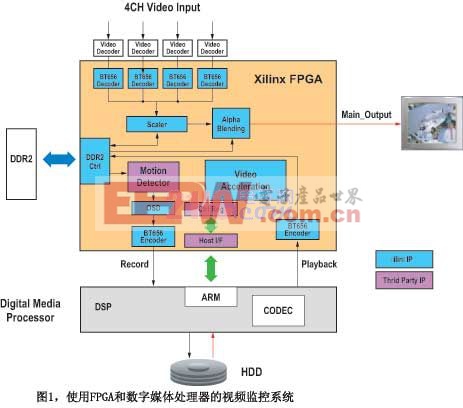

使用低成本的 Xilinx FPGA,可以更进一步提供运动探测、视频缩放、颜色空间转换、硬盘接口和DDR2存储器接口,还可以将两个 27MHz ITU-R BT656 数据流时分多路传输到一个 54MHz 数据流中,同时为 DSP 处理器提供视频加速。要将两个 ITU-R BT656 数据流多路传输到一个 ITU-R BT656 数据流中,仅需要一个通道视频端口来独立地传输完整的二通道视频数据。要为只有一个 ITU-R BT656 视频输入端口的数字媒体处理器提供接口,这种实现方法非常有用。图 1 所示就是这样一种建议架构的框图。

评论