模数转换技术及其发展

当前,为了适应计算机、通讯和多媒体技术的飞速发展以及高新技术领域的数字化进程不断加快,ADC在工艺、结构、性能上都有了很大的变化,正在朝着低功耗、高速、高分辨率的方向发展。

1 ADC的主要类型

目前,世界上有多种类型的ADC,有传统的并行、逐次逼近型、积分型ADC,也有近年来新发展起来的∑-Δ型和流水线型ADC,多种类型的ADC各有其优缺点并能满足不同的具体应用要求。低功耗、高速、高分辨率是新型的ADC的发展方向,同时ADC的这一发展方向将适应现代数字电子技术的发展。

任何ADC都包括三个基本功能:抽样、量化和编码。抽样过程将模拟信号在时间上离散化,使之成为抽样信号;量化将抽样信号的幅度离散化使之成为数字信号;编码则将数字信号最弹簧表示成数字系统所能接受的形式。如何实现这三个功能就决定了ADC的形式和性能。同时,ADC的分辨率越高,需要的转换时间就越长,转换速度就越低,故ADC的分辨率和转换速率两者总是相互制约的。因而在发展高分辨率ADC的同时要兼顾高速,在发展高速ADC的同时要兼顾高分辨率,在此基础上还要考虑功耗、体积、便捷性、多功能、与计算机及通讯网络的兼容性以及应用领域的特殊要求等问题,这样也使得ADC的结构和分类错综复杂。目前, ADC集成电路主要有以下几种类型。

1.1 并行比较ADC

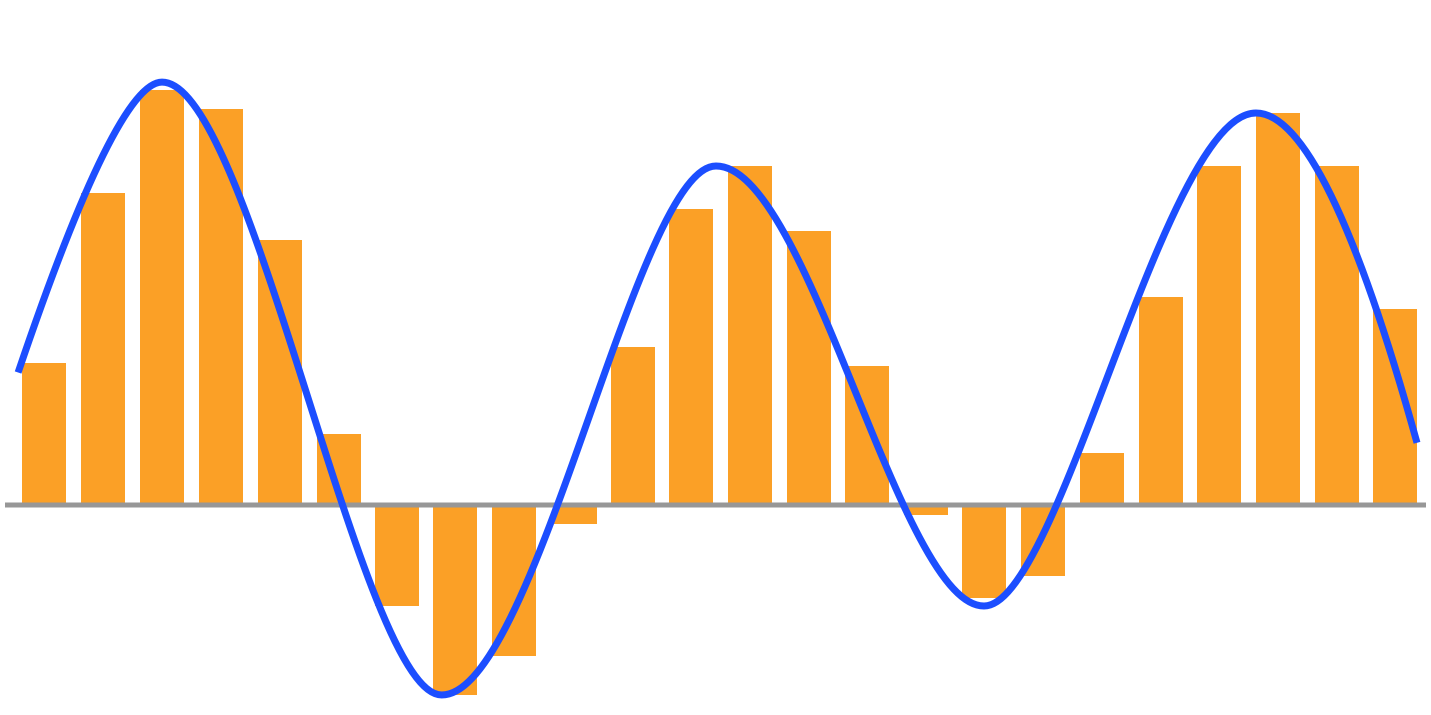

并行比较ADC是现今速度最快的模/数转换器,采样速率在1GSPS以上,通常称为“闪烁式”ADC。它由电阻分压器、比较器、缓冲器及编码器四种分组成。这种结构的ADC所有位的转换同时完成,其转换时间主取决于比较器的开关速度、编码器的传输时间延迟等。增加输出代码对转换时间的影响较小,但随着分辨率的提高,需要高密度的模拟设计以实现转换所必需的数量很大的精密分压电阻和比较器电路。输出数字增加一位,精密电阻数量就要增加一倍,比较器也近似增加一倍。例如,n位的ADC需要2n个精密电阻和2(n-1)个并联比较器。分压电阻网络彼此相差1个最低有效位VR/2n,如图1所示。

闪烁式ADC的分辨率受管芯尺寸、过大的输入电容、大量比较器所产生的功率消耗等限制。结果重复的并联比较器如果精度不匹配,还会造成静态误差,如会使输入失调电压增大。同,这一类型的ADC由于比较器的亚稳压、编码气泡,还会产生离散的、不精确的输出,即所谓的“火花码”。这类ADC的优点是模/数转换速度最高,缺点是分辨率不高,功耗大,成本高。

现代发展的高速 ADC电路结构主要采用这种全并行的ADC,但由于功率和体积的限制,要制造高分辨率闪烁式ADC是不现实的。由两个较低分辨率的闪烁式ADC构成较高分辨率的半闪烁式ADC或分级型ADC是当今世界制造高速ADC的主要方式。图2所示是一个8位的两级并行半闪烁式ADC的原理框图。其转换过程分为两步:第一步是粗化量化。先用并行方式进行高4位的转换,作为转换后的高4位输出,同时再把数字输出进行D/A转换,恢复成模拟电压。第二步是进一步细化量化。把原输入电压与D/A 转换器输出的模拟电压相减,其差值再进行低4全的A/D转换。然后将上述两级A/D转换器的数字输出并联后作为总的输出。这样,在转换速度上作出了一点牺牲,但解决了分辨率提高和元件数目刷增的矛盾。现代高速ADC与普通ADC相比的主要特点是:单电源性能;将基准电源、采样保持器和增益放大器集成在一块芯片上,集成度高;采用标准的0.6μm的CMOS工艺开发各种价格的低功耗ADC。

1.2 逐次逼近型

逐次逼近型ADC是应用非常广泛的模/数转换方法,它由比较器、D/A转换器、比较寄存器SAR、时钟发生器以及控制逻辑电路组成,将采样输入信号与已知电压不断进行比较,然后转换成二进制数。其原理图如图3所示,首先将DAC的最高有效位MSB保存到SAR,接着将该值对应的电压与输入电压进行比较。比较器输出被反馈到DAC,并在一次比较前对其进行修正。在逻辑控制电路和时钟驱动下,SAR不断进行比较和移位操作,直到完成LSB的转换,此时所产生的 DAC输出逼近输入电压的

评论