机载数字视频记录系统方案设计

1 系统总体设计与工作原理

本文引用地址:http://www.amcfsurvey.com/article/165235.htm本系统的主要目标之一是实现系统的小型化,为此采用硬件压缩,核心芯片采用zepax公司的sz1510高性能压缩编码芯片。sz1510可工作于mjpeg、mpeg-1编码以及vcd格式的视频编码等多种模式,mjpeg编码图像质量很好,但码率很高,需大容量的磁盘存储器,由于磁盘存储器对工作环境要求较高,在机载环境下若采用磁盘存储器则必须增加相应的减震、恒温等防护设备,从而导致体积大大增加,而mpeg-1编码压缩比高,码率相对较低,且图像质量满足实际需要和系统设计要求,因此本系统选用mpeg-1编码方案,同时,通过采用大容量的半导体存储器,大大减少了系统的体积,提高了系统的抗震性、可靠性,实现了系统的小型化。

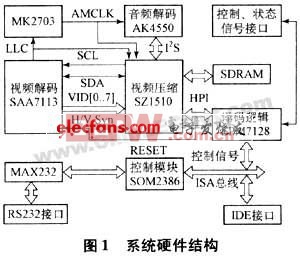

系统的总体结构如图1所示,硬件电路主要包括视频音频解码单元、压缩编码单元、译码逻辑及接口单元、

控制单元、存储单元5个部分。

系统上电后,som2386初始化音视频编码模块,系统正常启动后,saa7113对输入的复合视频信号进行解码,生成ccir-601数字视频流,ak4550采集输入的模拟音频信号,生成pcm数字音频流,分别送入压缩编码芯片sz1510,压缩成mpeg-1系统流后,在som2386控制下以文件形式存储到电子硬盘。

2 硬件设计

为提高系统的可维护性及降低维修成本,本系统硬件结构采用模块化的设计方法,系统分为3个模块:

a)视频音频解码及压缩编码模块:包括saa7113、mk2703、ak4550、sz1510、sdram;

b)逻辑连接、转换及接口模块:包括epm7128、max232、rs232接口、ide接口、控制、状态信号接口;

c)控制及存储模块:包括som2386和电子硬盘。

各模块分别做成相对独立的电路板,模块间用接插件相连,若系统中某个模块出现故障,只需更换该模块,不必更换整个系统,有利于节约时间和降低成本。

2.1 视频音频解码及压缩解码部分设计

视频解码器采用philips公司的saa7113,是一种可编程视频处理芯片,通过简单的i2c总线可对其实现编程控制,具有4路视频输入、抗混叠滤波、自动钳位和增益控制、多制式解码以及亮度、对比度和饱和度控制等功能,为系统设计带来极大的方便,它对输入的pal制式复合视频信号进行采样,解码后生成8bit/象素的ccir-601数字视频流(颜色空间为ycbcr,取样为4:2:2),送到视频压缩芯片sz1510的数字视频输入接口,它的输入时钟由24.576mhz的有源晶振提供,为sz1510提供场同步信号vs和行同步信号hs,同时,27mhz的像素时钟分为两路:一路直接输出至sz1510,作为其内部的数字视频的采样时钟;另一路通过锁相环时钟芯片mk2703降为48khz时钟amclm,作为音频编解码芯片ak4550的系统时钟,以实现视频和音频的准确同步,sz1510利用其gpio接口模拟的i2c总线对saa7113进行初始化。

音频解码器采用ak4550,它对模拟音频进行高信噪比16bit数字采样,生成pcm数字音频流。

压缩编码由芯片sz1510和视频帧缓存sdram(1m×16bit)组成,sz1510是一款高性能的mjpeg、mpeg-1编码芯片,支持多种工作模式和比特率模式,内部主要由视频编码核、tms320c54x高性能dsp核、接口电路、dma控制器和时钟产生电路等组成,视频编码核的结构如图2所示。

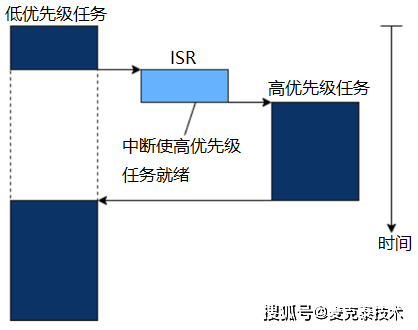

sz1510对输入其内部的视频流首先经过视频预处理、自动裁减、 场景切换检测,转换为cif格式的视频帧,然后,经过运动估计、运动补偿,离散余弦变换/反离散余弦变换和可变长编码等处理,生成mpeg-1视频基本流并存储于sdram中,同时,dsp核完成mpeg-1音频编码以及mpeg-1格式的音/视频的组合,生成mpeg-1格式的系统流,然后经过输出端口大小为256b的fifo缓冲进行数据的输出,正常工作时,当fifo满时就产生一个frdy(fifo读)中断通知主机读取fifo中的数据,主机通过z56次读data_out寄存器完成数据的读取,当sz1510发出一个eod(数据结束)中断时,数据传输结束。

评论