新一代芯片专享的定制数字版图设计

本文详细说明了一家消费类产品市场中大型无晶圆半导体公司的数字IC设计团队如何活用标准化工具的互操作性,以维护大型、讲求性能的40纳米设计的手工版图优势。该团队已经在多家供应商工具的协助下,通过Silicon Integration Initiative(Si2)的OpenAccess(OA)互操作性标准化成果有效展开整合,从而形成了具有更大生产力的定制IC版图流程。

本文引用地址:http://www.amcfsurvey.com/article/164871.htm大型数字集成电路(IC)设计的版图通常都是使用高度自动化的版图与绕线(APR)工具而建立的。尽管使用APR取代定制版图存在着许多争议,然而对大多数设计而言,APR的速度与掌握度等优势依然胜过面积或效能上的牺牲;但是,需要最高效能或最小面积的设计仍然依赖“手工”运用定制IC版图方法来完成。

在新一代的定制芯片中,复杂的规则、紧迫的上市时程以及纤薄尺寸与设计复杂度,使整个定制数字区块的设计越来越难以实现。全自动化的APR流程无法提供必要的版图与绕线的互动掌控。设计人员需要高度自动化而且可控制的全定制数字IC设计流程,获致最佳的性能、速度与面积。

定制设计中可控制式自动化的好处

在设计大量储存解决方案时,多年来设计团队都是为自己的模拟与定制数字设计而部署定制IC版图自动化。虽然模拟设计人员一直都使用定制设计方法,但数字设计团队通常只有性能、功耗、速度或面积要求超过APR工具的能力时,才会转而使用定制设计工具与流程。

为了实现最佳性能与周转时间,工程师们会使用采用先进可控制式自动化技术的工具,更快速且更事半功倍地建立定制数字设计。包括先进的电路图导向版图(SDL)流程,这个流程运用具备高度可架构性、不依存于制程的参数式单元技术与器件层floorplan工具,提供实现最佳效能与密度所需的速度与控制,而不必改变设计风格或牺牲成果质量。

工程师们运用继承自电路图的联机而自动产生飞行线(flight lines),然后使用内建的规则导向交互式绕线器,手工配置关键网络的线路,以满足超过2GHz的严苛频率速度要求。在这种效能水平下,个别网络的绕线对于环境以及与其他绕线、网络甚至层别之间的互动会很敏感。为了平衡这些元素,设计团队必须与设计环境中所有元素互动。手工绕线时,设计团队可以安排路线、萃取与评估关键网络以实现绝佳时序,然后加以修改,直到获得所需值。

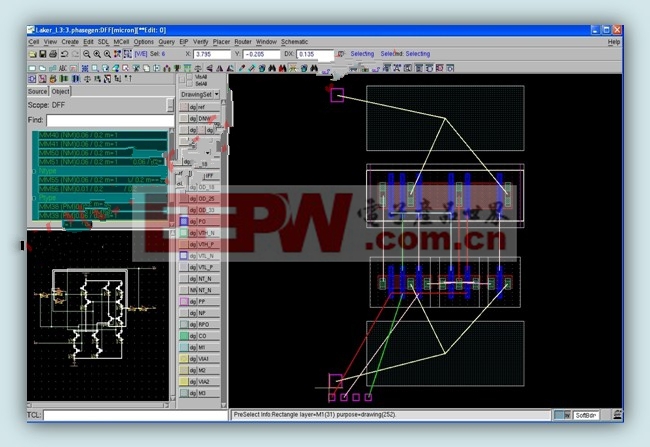

图1. 飞行线显示链接,并导引规则导向的手工绕线

迎接新一代定制数字设计的挑战

尽管定制版图与手工绕线作法能够满足效能需求,却越来越难在合理期间内完成新一代定制数字区块。

随着设计益趋庞大而且复杂,版图设计人员遭遇严重的绕线问题,并发现自己是在一片未知领域中设计绕线通路,必须放弃密度以便使越来越庞大的区块中的手工与点对点自动化绕线作业获得妥善的管理。虽然设计团队仍然能够达成能效目标,却常常要付出增加面积的代价,这在讲究成本的市场上不能令人满意。此外,完成设计所需的时间也远远超过单一版图所需时间。

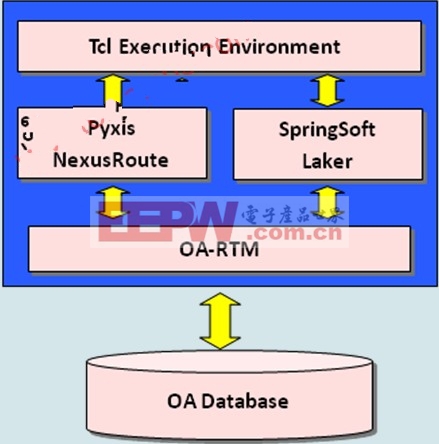

图2. OpenAccess中的相互操作性

随着设计团队转移到40nm制程以满足日增的效能需求,挑战也水涨船高。对于手工绕线与既有的自动化定制绕线解决方案而言,在这个制程中,模块变得过于庞大(太多互连线),而且设计规则也太先进。没有任何大规模定制绕线器能够提供先进制程所需的深亚微米DRC-clean与DFM-aware绕线技术。

刚开始的时候,设计团队尝试使用混合式流程,使用版图编辑器像以前一样以手工进行关键网络的绕线工作,然后运用APR支持先进DRC规则的数字绕线器来完成非关键网络。很不幸地,不断地换用多种工具降低了生产力。无论个别步骤的效率有多高,定制与数字设计领域还是无法密切配合。此外,这个方法并非交互式的,会导致团队损失层次与连接数据。自动化绕线器多半会反复执行部分精心绘制的关键网络的绕线,需要广泛的手工校对,甚至要绕线器重复作业。因此,设计团队要花6个星期时间反复作业,才能够获得可接受,却不是最佳的结果。

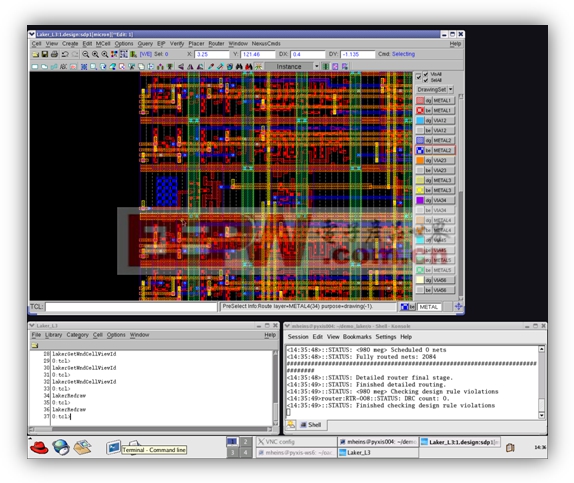

图3. 绕线器辨识障碍然后绕线

评论