FC-AL系统中FPGA的弹性缓存设计

引 言

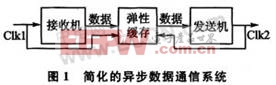

本文引用地址:http://www.amcfsurvey.com/article/163266.htm一个简化的异步数据通信系统如图1所示。接收机端从接收到的来自串行链路的比特流中提取时钟信号Clk1,作为其工作时钟源;而发送机端采用本地晶振和锁相环产生的时钟Clk2,作为其工作时钟源。接收机在时钟Clk1的上升沿把数据写入弹性缓存,发送机在时钟Clk2的上升沿从弹性缓存中读出数据,从而实现数据的同步。

虽然光纤通道仲裁环中的所有通信设备必须工作在同一频率,但图1中两个不同源的时钟信号Clk1和Clk2除了在相位上可能存在差异外,由于制造工艺的因素,晶振产生时钟时其频率也是被允许有一定误差存在的。这个误差范围为±100×10-6,即在每一百万个理想时钟周期的时间内容许±100个时钟周期的偏差。两个不同的晶振产生同一频率的时钟时,它们之间可能存在的误差最大为200×10-6。所以,对于由不同晶振产生的同一频率的2个时钟,除了相位上的不同外,在最坏情况下,经过106/200=5 000个周期后,它们之间将出现一个时钟周期的偏移。对于连续的数据流,由于用于时钟同步的弹性缓存的大小有限,如果不能正确处理这个时钟周期的偏移,将会导致缓存溢出,损坏有效数据,严重影响系统的性能。

1 FC-AL弹性缓存管理的基本原理

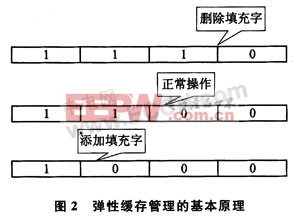

FC-AL通信系统中,也采用弹性缓存来解决数据在不同时钟域的同步问题,并通过对弹性缓存的管理适时地向缓存中添加或删除填充字,以控制缓存中有效传输字的数量(本设计中弹性缓存的存储单位为字),从而达到对时钟倾斜的补偿。填充字是FC-AL协议中定义的一类特殊的传输字,它们在帧与帧的间隙,且在帧界定符之外被传输。所以,弹性缓存的管理对这些特殊传输字进行的适当的添加或删除操作,不会损坏数据帧或影响环网的正常运作。何时对弹性缓存添加或删除填充字,是由缓存的占用率来决定的。弹性缓存空间的使用状态分为4个等级:添加填充字等待、保持状态、低级别的删除填充字等待以及高级别的删除填充字等待。当弹性缓存的写时钟慢于读时钟时(如图1中Clk1的频率略低于Clk2的频率),缓存可能被读空而出现误读,此时需要添加填充字,相当于增加缓存中可读的数据量,防止缓存出现下溢;当弹性缓存的写时钟快于读时钟时(如图1中Clk1的频率略高Clk2的频率),缓存可能出现被写满导致错误的数据覆盖,此时需要删除填充字,以增加缓存中的可用空间防止缓存出现上溢。

弹性缓存管理的基本原理如图2所示。假设弹性缓存的深度为4,图中被标识为0或1的每一个小格代表弹性缓存的一个存储空间。置1,表示相应的存储空间已被写入有效数据,且未被读出;置0,表示相应的存储空间未被写入,或写入的数据已被读出。

由于对于缓存的读操作必须是在有数据已写入缓存后才能开始,假设当缓存中有2个空间被写入时才开始读操作。所以,对于随后的弹性缓存管理,当缓存中刚好有2个空间被占用时,其处于保持状态,执行正常的读写操作;当缓存中超过2个的空间被占用时,其处于删除填充字等待的状态,说明写时钟的频率高于读时钟的频率,需要进行删除填充字的操作;当缓存中少于2个空间被占用,其处于添加填充字等待状态,说明写时钟的频率低于读时钟的频率,需要进行添加填充字的操作。

2硬件电路设计

用异步FIFO实现弹性缓存的关键是监测缓存空间的占用率,以此来判断读写时钟可能存在的微小差异,预见弹性缓存可能出现读空还是写满,并决定在何时进行填充字的添加或删除操作,以及何种等级的删除操作,并保证在添加或删除操作之后不对其后的数据读写产生任何影响。需要注意的是,这里的添加或删除填充字的操作都必须在读时钟域进行。

在异步数据通信系统中,使用弹性缓存实现数据在多时钟域之间的同步存在两个问题――数据延时和缓存大小。数据延时指的是,数据从被写入缓存到从缓存中读出的时间差。假设弹性缓存的大小为N,在不出现数据覆盖的前提下,当前数据被写入缓存的第N个存储空间,而此时缓存中还有N-1个空间中的数据还未被读出,至少在读时钟域看来是这样的,那么当前被写入的数据需要至少N-1个读时钟周期的延时后才能被读出。由此可见,缓存空间越大,经过缓存的数据的延时可能越大。但是,为了防止缓存将满或将空而添加或删除填充字的操作不能得到及时的执行而致使缓存溢出,须设置较大的缓存空间,给缓存管理提供较充足的时间范围,从而减小了缓存出现溢出的可能性。

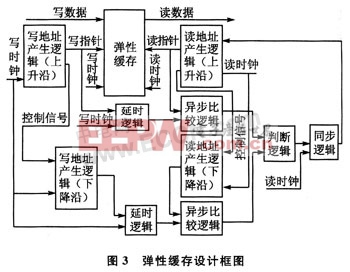

为了获得尽可能小的数据延时,同时不对数据的正常传输产生影响,在缓存大小满足系统基本要求的情况下,如何更精确地判断弹性缓存空间的占用率就变得很重要了。为了提高缓存管理的精度,本文中所采取的弹性缓存的设计方法如图3所示。在写时钟的上升沿将数据写入到基于写时钟上升沿的写地址产生逻辑的输出,即写指针所指向的弹性缓存空间;在读时钟的上升沿将基于读时钟上升沿的读地址产生逻辑的输出,即读指针所指向的弹性缓存空间的数据读出。此外,还各设置了一个基于时钟下降沿的读和写地址产生逻辑,但它们不对弹性缓存的读写操作产生影响。分别对基于读时钟上升沿的读地址和经过延时后的基于写时钟上升沿的写地址,以及基于读时钟下降沿的读地址和经过延时后的基于写时钟下降沿的写地址进行异步比较。综合两个比较结果,判断因同频但不同源的读写时钟之间可能存在的差异而导致的弹性缓存空间占用率的变化。判断得到的异步信号通过一个同步逻辑被同步到读时钟域,控制基于读时钟上升沿的读地址产生逻辑的输出,从而实现对弹性缓存中填充字的添加或删除,达到预防缓存出现溢出的目的。

3仿真结果分析

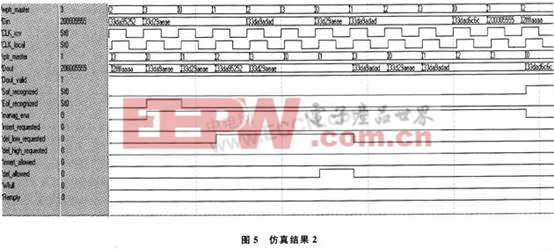

用Verilog语言实现图3所示电路的RTL描述,并对其用ModelSim进行仿真,仿真结果如图4和图5所示。两图中,CLK_rcv和CLK_local分别为频率非常相近的缓存的写时钟和读时钟。

图4中,CLK_rcv的时钟频率略低于CLK_local的时钟频率,弹性缓存有被读空的可能。当CLK_local比CLK_rcv多出半个时钟周期左右后,缓存管理就发出添加填充字的请求,以在最近的帧间隙进行添加操作。

图5中,CLK_rcv的时钟频率略高于CLK_local的时钟频率,弹性缓存有被写满的可能。当CLK_local比CLK_rcv少了半个时钟周期左右后就发出较低级别的删除填充字的请求,以在最近的间隙进行删除操作。若低级别的删除操作未被及时执行,致使缓存空间占用率进一步提高,则请求较高级别的删除操作。

从图4和图5中可以看出,添加填充字,即在当前时钟周期不读缓存空间的数据,而是发送一个当前填充字;删除填充字,即在条件满足的情况下跳过当前读地址空间,直接读取下一个地址空间中的数据。

结 语

本文提出的弹性缓存设计方法,充分利用了光纤通道协议的特性,通过提高对弹性缓存的管理精度,减小了数据在弹性缓存中可能的最大延时,有利于提高仲裁环网的整体性能。

评论