基于STD总线的多路数字I/O设计

1 STD总线

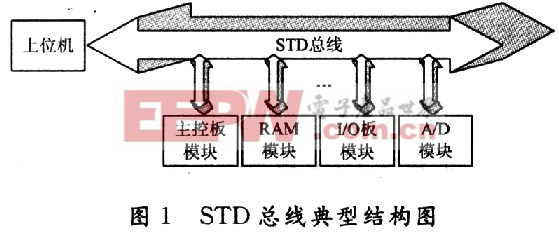

目前,STD标准总线已成为工业控制领域内最流行的标准总线之一,主要用于8位微处理机和单片机工业控制系统。STD总线的典型结构如图1所示。

在工业控制系统的实际应用中,上位机、主控模块等往往需要通过STD总线,根据STD总线的协议、特性访问其他的单片机系统。例如,在某测量设备中,上位机、主控模块可以通过总线上的I/O模块、A/D模块接口,采集传感器的量值,通过STD总线访问RAM模块,以及通过STD总线进行主控模块与总线上其他控制器之间,主控模块与上位机之间的通信与数据交换等,构成了一个微型的工业控制网络。本文的多路数字I/O就是STD总线中的一个模块。

2 多路数字I/O的硬件设计

2.1 电路组成

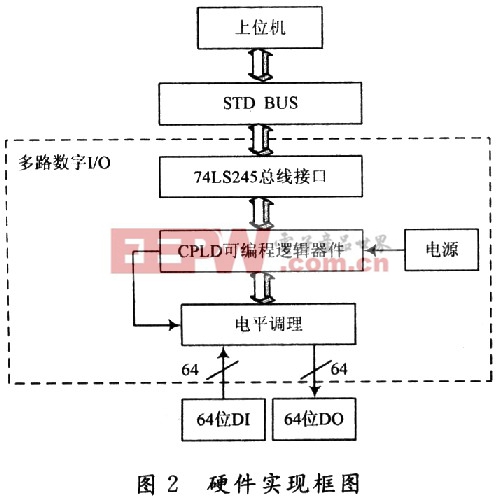

主要由可编程逻辑电路、电平调理电路、总线接口电路以及电源电路等组成。可编程逻辑硬件采用Xilinx公司的CPLD器件XC95288,应用。Xilinx公司的Project Navigator(ISE)集成开发环境进行编程开发;电平调理电路采用74LS245,具有输入输出电平转换的功能,还可以通过接继电器或者光电隔离器与外设接口;总线接口电路采用74LS245,对74LS245的DIR(方向)进行读写编程,实现了与STD总线的数据通信,电源电路为CPLD以及电平转换电路等提供必需的电源系统。

硬件实现框图如图2所示,虚线框内为多路数字I/O的硬件电路部分。

2.2 性能特点

数量多 CPLD芯片XC95288具有208个管脚,其中用户I/O管脚数量达到168个,除了地址总线、数据总线以及片选信号等所占用40个I/O之外,其余的128个I/0完全可以作为通用I/0编程使用;

面积小 如此众多数量的I/O,完全由一片CPLD来实现,简化了电路设计程序,减少了PCB的设计面积,又提高了数字I/O的稳定性;

灵活性高 由于每一个I/O都可独立编程,因此在使用过程中变得非常灵活,可以根据现场需求随时改变其输入、输出,在工业控制应用领域为产品的增强与升级提供了极大的灵活性。

此外,该设计还具有传输速度高(由CPLD的传输特性决定)及电平兼容性好等特点,可满足用户在测试、控制及设计应用中的多种需求。

3 多路数字I/O的程序设计

该系统使用业界领先的FPGA设计环境XilinxISE,其将先进的技术与灵活性、易使用性的图形界面结合在一起,可以在最短的时间,获得最佳的硬件设计。XC95288 CPLD是低功耗3.3 V器件,288个宏单元,6 400个可用逻辑门,168个用户I/O,再加上灵活、高度优化的VHDL硬件描述语言,实现了128位数字I/O的程序化设计。

评论