支持ONFI同步模式的NAND Flash控制器设计

摘要:先对ONFI标准进行了介绍,然后再设计了一种支持ONFI2.1标准源同步高速模式的NAND Flash控制器,包括状态机的设计,接口的设计等。对设计中遇到的源同步模式下,信号的对齐问题进行了说明,并提出了一种解决方法。同时设计中还会遇到数据跨时钟域传输的问题,本文也给出了解决办法。最后仿真和综合结果表明,本文的设计完全满足标准要求,具有实际的使用价值。

关键词:非易失闪存技术;ONFI2.1;源同步;两倍数据率;超大规模集成电路

0 引言

在当今的数字信息时代,人们对大容量数据存储的需求日趋旺盛。作为非易失性存储器的NAND Flash,由于其高容量低成本的特点,逐渐在实际产品,比如固态硬盘、智能手机、平板电脑等消费类电子产品中得到应用。

由于其特殊的内部结构,NAND Flash的操作方式与NOR Flash不太一样,不支持随机字节访问,其读、写操作均要以页面(Page)为单位进行,同一页面在未擦除前不允许进行多次写操作;而擦除操作必须以块(Block)为单位进行。因此,需要针对这一特性设计专用的控制器来完成各种操作。

本文根据这一目的,设计了一款NAND Flash控制器。该控制器不仅能够完成前面提到的基本操作,还能支持ONFI2.1标准中的同步接口模式。使其能够以200MB/s的速度对NAND Flash设备进行读写操作,远远快于其他同类NAND Flash控制器。

1 ONFI标准

ONFI(Open NAND Flash Interface,开放式NAND闪存接口)规范是一种Flash闪存接口的标准,它是Intel为统一当初混乱的闪存接口所倡导的标准。因为在此之前,市场上销售的NAND闪存芯片在引脚定义上都不完全相同。这就使得为一家公司设计的控制器,很有可能无法用在另一家公司的产品上。比如为东芝芯片设计的控制器,就无法用在三星或海力士的产品上,这就给上游的主控设计商以及最终的产品设计人员带来了很大的困难。

为此,Intel联合多家NAND Flash厂商制定了ONFI标准,统一NAND Flash芯片的引脚定义,并在此基础上采用新的技术以实现新的功能。2006年发布了ONFI1.O标准,使得接口的统一迈出了实质性的一步。但是该版本速度较慢,最高速度只有34MB/s,不具有太大的竞争优势。为了提高速度,ONFI组织在2008年发布了ONFI2.0,将接口速度提升到了133MB/s。在该版本中,主要是通过两项技术来提高传输速度。第一项就是在DRAM领域里常用的DDR(Double Data Rate,两倍数据率)信号技术。第二项是使用源同步时钟来精确控制锁存信号,使其能够达到更高的工作频率。2009年,ONFI组织又推出了规格更高的ONFI2.1标准,把最高速度提高到了200MB/s。

2 控制器结构

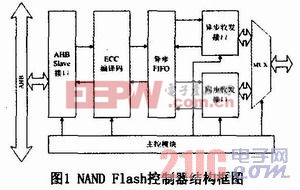

本文设计的NAND Flash控制器是SOC芯片的一部分,作为AHB Slave被挂在总线上,接收来自CPU的读、写和擦除等命令。其结构框图如图1所示。

其中AHB Slave接口模块主要是负责处理与AHB总线协议相关的操作;ECC编译码模块主要是负责对存入NAND Flash中的数据进行纠错编码和对从NAND Flash中读出的数据进行纠错码译码的工作;异步FIFO模块用来缓存数据,并承担数据跨时钟域的工作;主控模块负责整个控制器的控制;异步收发接口模块主要负责异步模式下的数据读写;同理,同步收发接口模块主要负责同步模式下的数据读写。本文的重点是与ONFI标准相关的接口设计,所以AHB Slave与ECC两个模块在此不再介绍,具体请参阅其他相关文献。

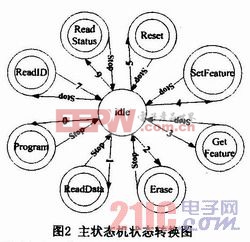

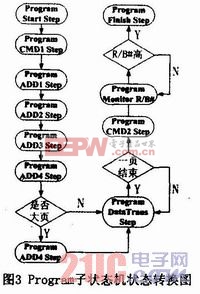

主控模块是整个控制器的中心控制模块,由一个主状态机和多个子状态机构成。主状态机有1个空闲状态和8个工作状态,分别对应着8种具体的操作。其状态转换如图2所示。而每个工作状态又对应1个子状态机,负责每个操作的具体细节。由于篇幅所限,本文只列出Program操作的子状态机状态转换图,如图3所示。其他子状态机的状态可以根据ONFI标准来确定。

评论