基于CPLD的图像传感器非均匀性校正

2. 1 硬件设计

目前,在非均匀性校正的硬件实现上,采用的都是1点或2点校正法. 电路由计数器、存储器、A /D转换器和D /A转换器等器件组成 . 通常,只能针对某个特定型号的图像传感器进行电路板制作,扩展性较差,而且,电路工作频率较低. 采用这些器件很难实现多点实时校正.

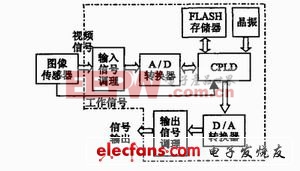

为了实现非均匀性多点实时校正,笔者设计了基于复杂可编程逻辑器件(CPLD)的校正系统. 该系统以CPLD EPM7512AE为核心,包括输入和输出信号调理电路、高速A/D采样单元、D/A转换单元和FLASH存储器等功能模块. 系统结构如图2所示.

图2 校正系统结构图

校正系统通过输入信号调理单元将接收到的图像传感器视频输出信号进行预处理,将信号调整到A/D转换器(ADC) TLV5580的采样电压范围内.系统控制核心CPLD接收图像传感器工作信号,根据视频信号串行输出的规律,产生控制TLV5580工作的时钟信号和转换数据输出使能信号,从而控制TLV5580对经过调理的视频信号进行采样量化,并将量化后的数字信号实时读入CPLD. 同时, CPLD 从FLASH存储器W29C040的相应单元中读出斜率和偏置校正系数,实现式(4)描述的校正算法,完成对各个视频信号的实时非均匀性校正.

CPLD还产生D/A转换器(DAC) TL5632C工作时钟信号,控制TL5632C将校正后的数字信号实时地转换成模拟信号,并由输出信号调理单元将该模拟信号调理为一个范围合适的电压信号作为校正系统的输出(即经过校正的视频信号).

2. 2 CPLD设计思想

作为控制核心的CPLD是一种半定制器件,它最大的优点就是采用编程的方式定制其具体实现的硬件电路,指定CPLD的硬件实现功能. 笔者主要采用硬件描述语言VHDL,并结合原理图方式在MAX + PLUSⅡ集成开发环境下进行CPLD 功能的设计. 采用VHDL语言的设计方法,可实现器件的无关性,并且功能实现灵活、修改方便. CPLD的应用以及VHDL设计方法的使用为校正系统能灵活地适用于不同图像传感器的校正以及实现不同的校正算法提供了可能和保证.

根据系统校正功能要求及工作流程, CPLD 实现的功能主要包括:

1) 分频器. 分频器对晶振信号进行分频,产生校正系统协调工作的时钟基准信号. 分频器采用VHDL进行设计,可以根据不同的晶振、不同的图像传感器工作频率,灵活、方便地选择不同的分频数,产生合适的时钟基准信号.

2) ADC控制信号发生模块. 该模块采用VHDL进行设计,根据分频器产生的时钟基准信号和图像传感器的工作信号,产生能够准确控制TLV5580工作的时钟信号和转换数据输出使能信号,保证TLV5580实时、准确地采集经过调理后的视频输出信号.

3) 地址发生器. 地址发生器产生读取FLASH存储器中斜率和偏置校正系数的地址信号. 由于每个光敏元在每个辐照度子区域有一组数据(一个斜率校正系数和一个偏置校正系数) ,为了方便读取,将同一辐照度子区域的所有光敏元的校正系数按照在图像传感器中的相对位置顺序存储. 所以,同一光敏元在不同子区域下的数据地址,高位地址不同,低位地址则完全相同;同一子区域内不同光敏元的数据地址,则高位相同,低位不同. 因此,地址发生器由2部分构成:高位地址发生器和低位地址发生器.

高位地址发生器实质上是一个比较器,确定当前图像传感器所测量的辐照度所处的子区域. 其设计思想是:将采集到的第1个光敏元的视频信号和预先设定的对应于每段辐照度子区域的边界值进行比较,根据比较的结果产生相应的高位地址. 由于采用并行执行的指令来实现,能够很好地满足实时处理的要求.低位地址发生器根据视频信号逐一串行输出的特点以及TLV5580工作特点(每个工作时钟采集1个光敏元的输出信号)进行设计,实质上是一个计数器,只需对TLV5580工作时钟信号进行计数,就能产生相应的低位地址.

4) 校正模块. 由乘法和加法2个子模块构成,分别采用MAX + PLUS Ⅱ提供的功能单元LPM_MULT和LPM_ADD_SUB来实现. 校正模块将采集到的视频信号以及从FLASH存储器读取的相应校正系数按照式(4)进行处理,实现图像传感器的实时非均匀性校正.

5) DAC控制信号发生模块. 产生控制TL5632C工作的时钟信号,指挥TL5632C实时地将校正后的数字视频信号转换为模拟信号.

由于非均匀性校正功能的实现对时序要求严格,在程序的设计中,一定要注意时序的合理性. 将程序编写出来后,首先进行了仿真实验,在得到期望的工作波形数据后,进行逻辑综合生成网络表和下载文件,最后将程序文件下载到EPM7512AE中,以便进行下一步对图像传感器非均匀性校正指标的测试.

3 实验结果

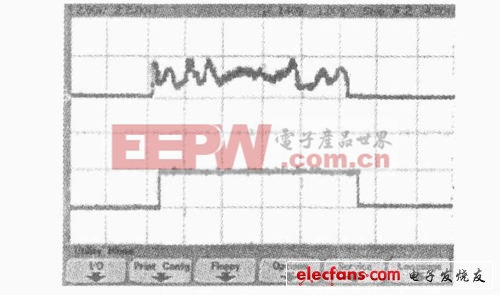

笔者以重庆大学研制的CL512J型自扫描光电二极管阵列( SSPA)图像传感器作为对象,进行6点非均匀性实时校正的实验. CL512J是一种具有512个光敏元的线阵列图像传感器. 其工作波形如图3所示,以起始脉冲S信号(低电平有效)表示每一次扫描输出的开始. 光敏元的视频输出电压Uo 与时钟信号CP同步,在CP的上升沿时刻开始输出,经过短暂的上升时间后,稳定下来;在CP为低电平时,输出变为0. 因此,将S和CP信号引入校正系统作为CPLD产生各种控制信号的基本依据.在实验中, 首先通过数据采集卡和计算机, 将 CL512J 的校正系数计算出来, 按指定地址保存在FLASH存储器中.

图3 CL512J工作波形

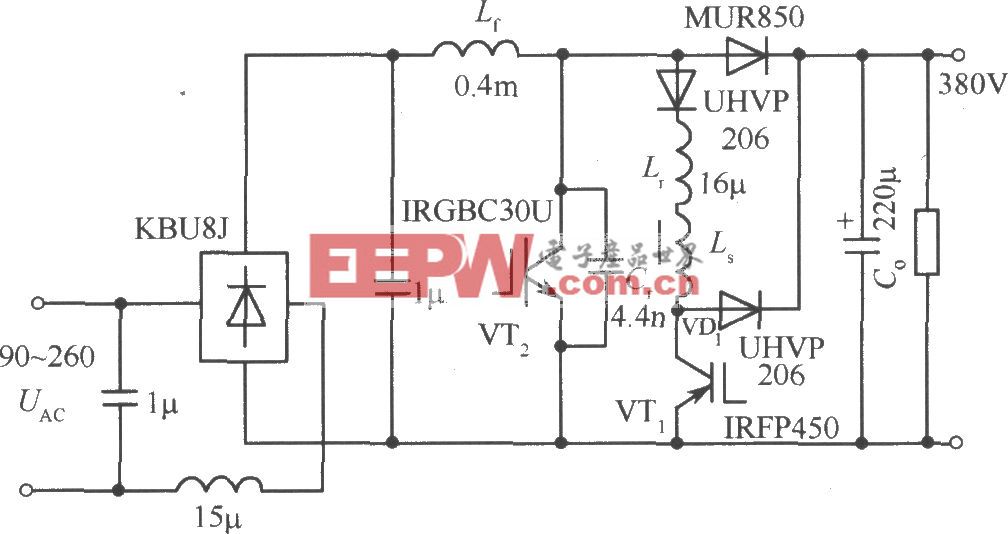

然后, 在MAX + PLUS Ⅱ开发环境下, 根据CL512J的具体情况(光敏元个数、工作频率、视频信号串行输出的特点等) ,设计出相应的程序,经过仿真验证后,将程序文件下载到CPLD中.最后,将CL512J的视频信号接入校正系统,并利用示波器观察校正前后的视频电压波形. 图4给出了一个实时校正的实验结果,上面一条曲线是CL512J实际的视频输出信号,下面一条是经过校正后的视频信号. 校正前, 输出信号最大值为2V, 最小值不足0. 8V,非均匀性超过40%. 校正后,电压信号在2V附近变化,非均匀性约为2%. 由于TLV5580等器件的工作特点,校正信号延迟约5个CP时钟后输出.

图4 不均匀性校正实验结果图

4 结束语

设计的非均匀性校正算法以及硬件校正系统,能够有效地实现图像传感器的多点实时非均匀性校正.采用CPLD作为核心构成的校正系统具有功耗低、抗干扰能力强、功能实现方便和扩展灵活等优点,能够有效地适用于多种图像传感器的校正.但是,由于存在光电转换曲线分段线性化误差、A/D转换器和D/A转换器等器件转换精度问题以及实验条件的限制等客观原因,影响了图像传感器非均匀性校正效果的进一步提高.

评论