超低抖动时钟合成器的设计挑战

该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动 100fs。分析和仿真结果表明,要达到这一抖动指标,设计难度远远高于预期。关于元器件变量和折衷方案的讨论为进一步的研究提供了线索。

概述

本文为高速数据转换器提供了一个低抖动时钟源的参考设计,目标是在时钟频率高达2GHz时,边沿间抖动 100fs。对于1GHz模拟输出频率,所产生的抖动信噪比SNR为:-20 × log(2 × π × f × tj) = -64dB。

设计需求

时钟设计的最高频率为2GHz,然而,一些VCO (压控振荡器)和预分频器能够将其扩展到更高频率,且不同器件能够扩展的范围也不尽相同。这里介绍的参考设计、仿真测试和结果只针对2GHz输出频率。

一些高速转换器采用时钟信号的两个沿作为内部定时。这就要求严格的50%占空比。另外,目标输出驱动能力是10dBm/50Ω,即2VP-P差分输出。

合成器设计基础

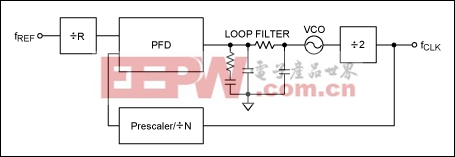

图1. 传统锁相环

最简单的设计是传统的锁相环电路,如图1。如上所述,要求严格的50%占空比。因此,VCO工作在目标时钟的两倍频(4GHz),然后通过2分频获得目标频率和占空比。由于分频器会引入抖动,所以将其置于锁相环环路以消除噪声。

环路滤波器提供对参考噪声的低通滤波和VCO噪声的高通滤波。同时,它也决定了环路建立时间。由于这是固定频率应用,环路建立时间不存在问题;滤波器带宽可只对噪声进行优化。窄带滤波器更容易处理参考噪声,但增加了VCO的噪声负担,宽带滤波器的效果则相反。

虽然我们需要在VCO和参考时钟两者之间进行平衡,通过对两者的研究表明,同时获得两者的最佳性能是可能的。100fs抖动的相噪指标决定了噪声将有多低。

相噪是相对于载频的指标,反比于频偏(dBc/Hz)。所有相噪的集合就是相噪功率,它用来和基频功率相比较。相噪除以基频功率得到抖动。

例如,假设2GHz VCO在10kHz到100kHz内具有-110dBc/Hz的SSB (单边带)相噪,其带宽为90kHz,结果为49.5dB。所以,总噪声为-60.5dBc。SSB噪声功率为:

所以,噪声电压有效值为:

根号里的系数2代表包括了两个单边带¹。

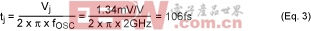

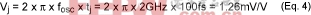

其抖动为:

式3只得出了10kHz至100kHz频偏的抖动,为了确定整体抖动,还要考虑其余频偏。

另一种方法是,我们从抖动倒推相噪。于是,对于2GHz时100fs的抖动:

SSB噪声功率为:

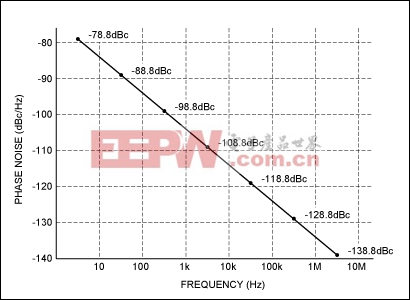

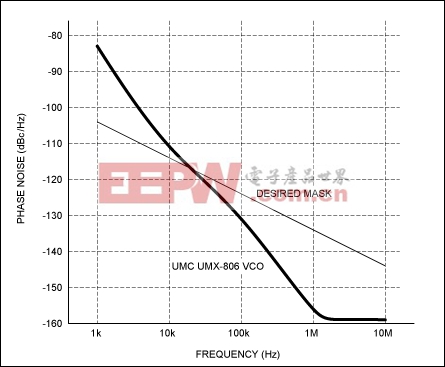

式5结果等效于-61dBc的总噪声功率(SSB)。如果假定相噪在1Hz到10MHz均匀分布,那么,换算成dBc/Hz,得到以下相噪模板(图2)。

图2. 相噪模板

毫无疑问,2GHz下抖动 100fs是一个非常不错的相噪值,特别是在10kHz至100kHz范围内。从图中可以看出,10kHz时的相噪大约为-114dBc/Hz。但很少有分离²的VCO能够达到这一水准,当然,集成VCO也很难达到这一目标。UMC (Universal Microwave Corporation)的VCO能够达到这一低噪级别。UMX系列产品的带宽为500MHz至5GHz,其10kHz相噪可以达到-112dBc/Hz以下。即使UMX系列中指标最差的VCO也满足我们的要求。

图3. UMX-806-D16对应于相噪模板的相噪

评论