无线传感器网络节点的研究与实现

无线传感器网络是新兴的研究领域,在军事、环境、健康、家庭、商业领域等许多方面有着巨大的潜在应用前景。无线传感器网络节点是组成网络的基本单元,无线传感器网络的迅速发展,给无线传感器网络节点的设计和管理提出了许多挑战。

无线传感器网络节点

无线传感器网络是集数据采集、处理及通信功能于一体的分布式自组织网络。无线传感器网络由在一定区域范围内的多个具有无线通信、传感、数据处理功能的网络节点组成。传感器节点负责采集、处理、压缩数据、中转其他节点的数据包并将数据包发送出去。在不同的应用中,传感器网络节点的结构不尽相同,一般由数据采集单元(传感器、A/D转换器)、数据处理和控制单元(微处理器、存储器)、无线通信单元(无线收发器)和供电单元(电池)等组成。

相对于传统无线网络节点,无线传感器网络节点具有明显的技术特点:(1)网络节点密度高,数量大;(2)节点的计算和存储能力有限;(3)节点体积微小,通常携带能量十分有限的电池,节点能量有限;(4)通信能力有限,传感器网络的通信带宽较窄,节点间的通信单跳距离通常只有几十到几百米,因此在有限的通信能力下如何设计网络通信机制以满足传感器网络的通信是必须考虑的问题;(5)各传感器节点位置随机分布,具有自组织特性。

由于无线传感器网络节点具有以上特点,在节点的设计上,要求节点硬件成本较低、必须低能耗、必须支持多跳的路由协议。 IEEE802.15.4/ZigBee协议充分考虑了无线传感器网络应用的需求,具有设备省电、通信可靠、网络自组织、自愈能力强、成本低廉、网络容量大、网络安全等特点。由这些基本要求,进行了支持802.15.4/ZigBee协议的无线传感器网络节点的硬件设计。

网络结构

节点可以组成三种拓朴结构:星型结构、网状结构(Mesh)和簇状结构(Cluster tree)。节点以自组织形式构成网络、每个节点都可以自主采集数据,数据通过单跳方式或多跳中继方式送到汇聚节点(Sink节点)。汇聚节点将收集的数据发送到远程的控制中心,或通过RS232接口把数据发送给PC 机进行数据处理和存储。

节点设计

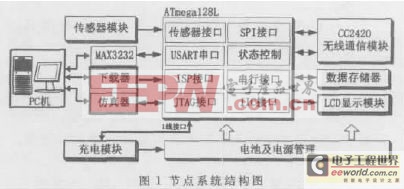

节点硬件采取模块化结构设计如图1所示,由运算及通信子板、传感器子板、充电及状态显示子板构成。运算及通信子板由微处理器、数据存储电路、无线通信模块、电源管理模块等组成,主要作用是储存、处理数据,完成节点间的无线通信并为系统提供能量。传感器子板由若干传感器组成,负责监测区域内信息的采集。充电及状态显示子板由充电模块和LCD液晶显示模块组成,用来显示节点电池充电情况节点的工作状态以及电池的电量。

微处理器电路

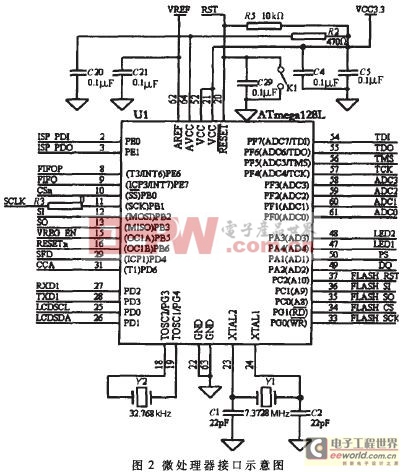

微处理器电路采用Atmel公司的ATmega128L微控制器,它采用低功耗CMOS工艺生产,基于RISC结构,具有片内128KB的程序存储器 (Flash)、4KB的数据存储器(SRAM)和4KB的EEPROM,有8个10位ADC通道、2个8位和2个16位硬件定时/计数器、8个PWM通道,具有可编程看门狗定时器和片上振荡器、片上模拟比较器、JTAG、UART、SPI、I2C总线等接口。ATmega128L可在多种不同模式下工作,除了正常操作模式外,还具有六种不同等级的低能耗操作模式,因此该微控制器适合于低能耗的应用场合。其接口示意图如图2所示。

ATmega128L 的工作时钟源可以选取外部晶振、外部RC振荡器、内部RC振荡器、外部时钟源等方式。工作时钟源的选择通过ATmega128L的内部熔丝位来设计,熔丝位可以通过JTAG编程、ISP编程等方式设置。本设计中ATmega128L采用两个外部晶振:7.3728MHz晶振作为ATmega128L的工作时钟;32.768kHz晶振作为实时时钟源。

数据存储电路

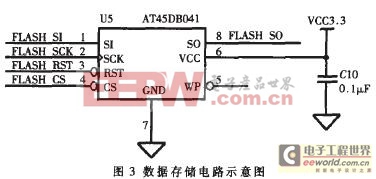

由于无线传感器节点的通信模块传输能力有限,加上节点工作的占空比非常小,很多数据不能实时转发出去,所以需要有一个可管理的存储器存储这些数据,暂存自己采集的或需要转发的其他节点采集来的数据。本设计选用512KB串行FLASHAT45DB041存储数据。与普通的数据存储器相比,该芯片具有功耗低、体积小、串行接口、外部电路简单等特点,适合传感器节点使用。数据存储电路示意图如图3所示。

无线通信模块

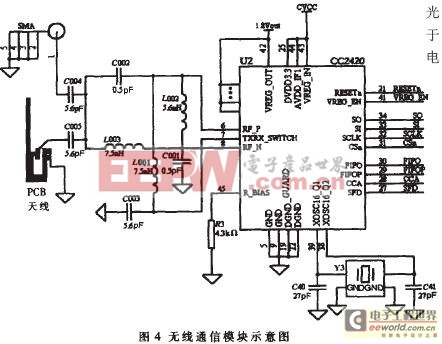

无线通信模块采用无线射频CC2420模块。它是Chipcon公司在2003年底推出的一款兼容2.4GHz IEEE802.15.4标准的无线收发模块,基于Chipcon公司的SmartRF03技术,使用CMOS工艺生产,工作电压低、能耗低、体积小,具有输出强度和收发频率可编程等特点。该芯片只需晶体振荡器及负载电容、输入/输出匹配元件和电源去耦电容等很少的外部元件即可正常工作,可确保短距离通信 的有效性和可靠性,其最大收发速率为 250kbps。

CC2420有33个16位配置寄存器、15个命令选通寄存器、1个128字节的发送FIFO缓存区、1 个128字节的接收FIFO缓存区、1个112字节的安全信息存储器。CC2420与处理器的连接比较简便,它使用SFD、FIFO、FIFOP和CCA 四个引脚表示收发数据的状态;处理器通过SPI接口(CSn、SO、SI、SCLK)与CC2420交换数据、发送命令,使用RESETn引脚复位芯片,使用VREG_EN引脚使能CC2420的电压调整器,使其产生CC2420所需要1.8V电压,从而使CC2420进入正常工作的状态;CC2420通过单极天线或PCB天线进行通信。其模块示意图如图4所示。

评论