复旦研制新型微电子器件半浮栅晶体管 有望提速CPU

复旦大学微电子学院副院长、国家02重大专项总体组专家张卫教授领衔的科研团队研制出一种新型的微电子器件——半浮栅晶体管(SFGT),可让数据擦写更容易、速度更快,操作电压更低,为设计低功耗芯片奠定了基础。相关研究成果刊登于8月8日出版的《科学》杂志上。这是我国科学家在该杂志上发表的第一篇微电子器件方面的论文。

本文引用地址:http://www.amcfsurvey.com/article/158947.htm据介绍,张卫教授团队长期从事集成电路工艺和半导体器件的研究。这一成果被业内学者称为将可能改变近年来IT业界所担忧的问题:技术的发展将使摩尔定律达到极限无法再突破。这也被认为是中国微电子产业的一个新机遇,有可能改变目前国内的芯片行业。

据团队成员王鹏飞教授介绍,金属-氧化物-半导体场效应晶体管(MOSFET)是目前集成电路中的主流器件,根据摩尔定律,芯片上的晶体管特征尺寸在不断地缩小,使得芯片上的晶体管数量每隔18个月便会增加一倍。过去几十年工艺的进步让MOSFET晶体管的尺寸不断缩小,越来越接近其物理极限。集成度的增加使得芯片功耗密度太大而面临散热困难。因此,业界一直尝试在材料和电路设计方面有所突破,同时积极寻找基于新结构和新原理的晶体管,突破现有的技术瓶颈。

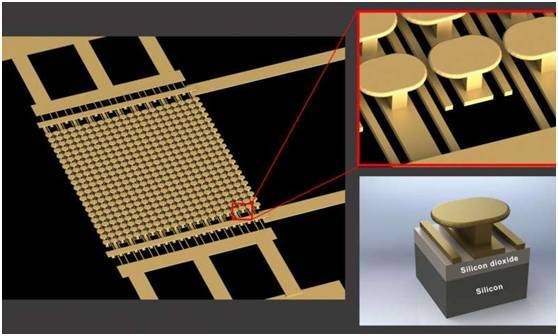

半浮栅晶体管的前瞻研究就在这种情况下展开。复旦大学的团队巧妙地把隧穿晶体管(TFET)和浮栅晶体管相结合,构成了一种全新的“半浮栅”结构的器件,称为半浮栅晶体管(SFGT)。这种晶体管的“数据”擦写更加容易、迅速,而且整个过程都可以在低电压条件下完成,为实现芯片低功耗运行创造了条件。

半浮栅晶体管在CPU的高速缓存(Cache)、DRAM和CMOS图像传感器等领域有很好的应用前景,且优势明显。比如CPU的高速缓存,现在通常采用6个MOS晶体管构成一个存储单元(SRAM),集成度低,占用面积大。在28nm英特尔XeonCPU中约一半的面积被迫交给缓存占用,极大地浪费了资源。如果采用复旦大学发明的半浮栅晶体管设计缓存电路,则单个晶体管即可构成一个存储单元,速度与传统6个MOS晶体管的SRAM存储单元相当,但缓存占用的面积可以缩减为原来的十分之一,且降低了功耗。

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理

评论