跳频电台中央控制单元及跳频单元的硬件设计

摘要:跳频技术具有很强的抗干扰性能,非常适用于战术电台。提出一种跳频电台的总体设计构想,用ARM+FPGA架构作为硬件平台系统,给出中央控制单元和跳频单元的硬件设计方案。

1 序言

跳频通信是扩频通信的一个分支,其工作原理是收发双方传输信号的载波频率按照预定规律进行离散变化,也就是说,通信中使用的载波频率受伪随机变化码的控制而随机跳变。它的突出特点是抗干扰能力强,具有较好的隐蔽性和抗截获性。

2 跳频电台的设计思路及参数

本跳频电台的设计初衷是利用最新的数字技术设计适合计算机数据通信的电台终端。根据现有条件和调研结果,采用了较为成熟和简单的编解码和同步方案。由于系统的硬件采用模块化设计,控制系统采用软件实现,因而为系统的技术升级,以及采用更优化的调制、信道编码和同步方案来实现最佳的系统性能提供了一个通用的硬件平台。

本项目设计的是自组织网网络跳频电台,跳速为4000跳/s(即每跳持续时间为250μs),跳频点数为50,网络最大节点数为16个,最大通信距离为300m。信息速率为2Mb/s,信道误码率为10-3。同步方案采用扫描驻留同步法,这是基于精确时钟法、同步字头法、自同步法的一种综合的同步方法。这种方法具有同步时间快、同步概率高、随机性好等特点,能够满足战场通信的各种要求,适用于中高速跳频系统。

3 硬件平台设计

跳频电台的结构和模块接口原理框图如图1所示。本文阐述的是中央控制单元模块和跳频单元模块(伪码发生控制器和频率合成器)的硬件设计。

3.1中央控制单元模块

3.1.1硬件平台设计

中央控制单元是基于ARM9的嵌入式系统,主要由S3C2410型嵌入式微处理器、存储系统和外部接口组成。S3C2410是Samsung公司推出的一款基于ARM920T内核的32位微处理器,资源丰富,带独立的16KB的指令Caehe和16KB数据Cache、LCD控制器、RAM控制器、NAND闪存控制器、3路UART、4路DMA、4路带PWM的定时器、并行I/0口、8路10位ADC、Touch Screen接口、I2C接口、I2S接口、2个USB接口控制器、2路SPI等,主频最高可达203MHz。利用S3C2410出色的内核性能和丰富的外部接口可构造一个嵌入式系统平台,用于跳频电台的中央控制。中央控制单元的硬件框图如图2所示。设计的中央控制单元的内部组件如下:

(1)核心处理器

在中央控制单元中,主CPU是Samsung公司的S3C2410。

(2)存储系统

主要由NAND Flash、SDRAM和NOR Flash组成。

NAND Flash是Samsung公司的SmartMedia卡,主要用于存放boot程序、操作系统镜像、应用程序及大容量的数据文件。本电台设计选用容量为64MB的K9S1208VOM。它与S3C2410的专门NAND Flash接口相连。

SDRAM是运行操作系统及各类数据的缓存,本电台设计选用Samsung公司的32MB K4S5616-32C,它是4M16bit4BANK的同步DRAM。本电台用2个K4S561632C实现位扩展,使数据总线宽度达到32bit,总容量为64MB。它的地址空间映射在S3C2410的BANK6。

NOR Flash是AMD公司的AM29LV800B,容量为1MB。NOR FLASH主要用于前期的调试和操作系统的下载。

(3)通用接口

利用S3C2410的IJSB口、简易JTAG口和标准串口与宿主机连接,进行操作系统的安装和应用程序的输入及调试。根据S3C2410的通用I/0模拟口性能来实现与伪码发生控制器和频率合成器的接口定义。

3.1.2功能及流程

中央控制单元是跳频电台的核心,由它提供各组件所需的控制信号,包括主CPU、数据缓存电路、数据存储与信息保存电路、逻辑控制电路等。主要实现以下功能:

MAC层控制协议实现,控制整个电台的T作;

中断处理:

开机自检:

接收来自外设接口单元的多种控制信息并实时处理这些信息;

控制FPGA产生跳频图案,并控制频率合成器的频率跳变;

产生阻塞信号,压制功放在换频期间的功率输出,以减少频谱溅射;

控制同步单元,实现跳频同步;

跳频参数、密钥信息的注入、存储与清除。

S3C2410主要控制数据输入/输出接口电路,完成与数据终端之间的数据交换。待发送的数据从数据终端设备经数据接口设备输入到S3C2410中。S3C2410将数据加上包头,封装成数据包,并对数据包进行CRC校验,将校验位加在包尾,然后将该数据包送到数字信号处理子系统以便进行调制和发送。在接收时,S3C2410对0FDM单元解调出的数据包进行CRC校验,判别数据包中是否有误码。若数据包正确,则将其中的数据帧通过数据输入/输出接口电路送给数据终端设备。由于采用的是数据分组通信,所以需要一些分组通信控制协议,同时还有自组织网的协议,这些协议都在S3C2410中执行。

3.2跳频单元模块

包括伪码发生控制器和跳频频率合成器,能产生所要的跳频图案及实现载波的高速跳变。

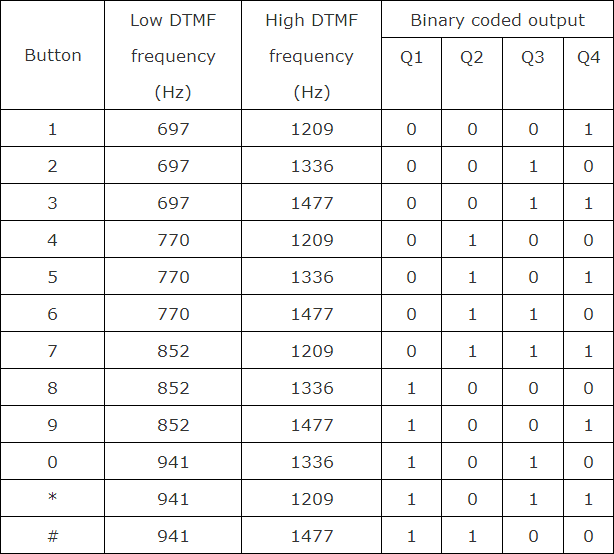

3.2.1伪码发生控制器

伪码发生控制器采用Ahera公司的EPlC3T144C8型现场可编程门阵列(FP-GA)和EPCS1。FPGA主要由TOD单元、密钥写入单元、PN码发生器单元、ROM单元及同步频率发生器单元组成。FPGA的单元结构如图3所示。

首先,TOD单元中的分频器对外部20MHz时钟进行l/50分频产生4kHz时钟,计数器通过对该4kHz时钟进行32bit计数,产生32bit频率为4kHz的本端TOD[31..0]信息;此TOD[31..0]和通过中央控制单元写入的密钥信息A [31..O]一起通过PN码发生器单元的首次相加运算、异或运算、置换运算和由再次相加运算产生6bit的PN码,然后和同步频率发生器单元产生的6bit码再通过中央控制单元控制的二选一控制器。根据不同通信时期的需要选择一种PN码作为ROM单元的地址码来读取ROM单元中预先存好的DDS 32bit频率控制字,同时与发送给DDS的时钟信号及片选信号一起传送给DDS来读取其相对应的跳频频率。在每次开机时,TOD[31..O]信息由本端中央控制单元通过读取本地时间信息进行转换和擦写TOD计数器产生。在初始同步阶段,发送端通过同步频率发送本端的TOD信息,接收端接收到发送端的TOD后.通过中央控制单元对本端的TOD计数器进行擦写,从而实现跳频图案同步。

3.2.2频率合成器

跳频的核心部件是直接数字频率合成器(DDS),本方案采用ADI公司的AD9954,它是采用先进的DDS技术开发的高集成度DDS,内置高速、高性能D/A转换器及超高速比较器,可作为数字编程控制的频率合成器,能产生200MHz的模拟正弦波。AD9954内含102432静态RAM,利用该静态RAM可实现高速调制,并支持多种扫频模式。AD9954可提供自定义的线性扫频操作模式,通过AD9954的串行I/0口输入控制字可实现快速变频且具有良好的频率分辨率。其应用范围包括灵敏频率合成器、可编程时钟发生器、雷达和扫描系统的FM调制源以及测试和测量装置等。频率合成器的原理框图如图4所示。

跳频序列采用截断的M序列方式,具体的实现在。FPGA中由程序完成。根据跳频码序列查找跳频图案表来获得所需产生的频率值,因为AD9954的频率控制寄存器是32位,所以从伪码发生控制器传来的是32频率控制字,频率控制字通过SPI总线传到AD9954后,先存人I/O缓冲寄存器中,然后通过I/0控制和SYNC_CLK(AD9954主时钟的4分频)共同作用将频率字送到频率控制寄存器中。32位频率控制寄存器的每32比特字都对应ROM单元中的一个确定频率,因为使用50个频点,所以输入的频率字有50种。由伪码发生控制器提供的40MHz频率经PLL单元后变为400MHz。然后把不同的输出频率存入ROM单元,ROM单元输出的数字信号经DAC后转换为模拟信号输出。

另外,由于AD9954输出的信号是差分信号,所以要在AD9954的输出端加一个l:1的不平衡一平衡变压器,将信号变成单路信号。而这时的信号还有很多毛刺,要经过一个滤波器滤波,采用120MHz的7阶椭圆滤波器来滤波。由此,DDS就产生了4000跳/s的跳变频率。

4 结束语

从整个硬件系统的设计来看,采用较多的数字设计技术。首先,采用直接数字频率合成器,简化了整个设计且提高了性能,同时DDS具有的高速频率切换性能为进一步提高频率跳变确定了可靠保证。其次,采用高性能的S3C2410微处理器和现场可编程门阵列,以嵌入式系统的方式为跳频序列的产生、同步的捕获与跟踪等处理过程实现了数字化和软件化,这样使得该跳频电台系统设计成为一个通用的数据通信硬件平台,为系统的进一步升级,采用性能更佳的同步方案和更具灵活性的组网方案创造了良好的条件。

评论