MIPS千兆网闸系统实现及仿真分析

关键词 千兆网 网闸技术信号完整性仿真

引 言

随着互联网的快速发展,网络安全问题日益突出。目前采用最多的网络安全措施是防火墙类软件,但防火墙类软件本身存在先天缺陷。防火墙隔离的网络是基于TCP/IP协议来进行信息交换的,而TCP/IP本身存在漏洞;同时防火墙的运行离不开操作系统,操作系统也可能存在未知的漏洞。采用网络隔离技术的网闸,能更有效阻断已知和未知的攻击,防范安全漏洞,隔离可信网络和不可信网络并能保持数据高效交换,从而提供更好的安全保护,是网络安全技术的发展方向。MIPS CPU作为RISCCPU体系结构的一种,无论是在高端的服务器还是在低端的嵌入式系统中,都得到了广泛的应用。对网络速度的要求、服务器的瓶颈、应用方式的变化,也在促使网络向千兆带宽发展。MIPS千兆网闸系统的开发对于现在及将来的网络安全意义重大。千兆网闸系统的PCB上有许多高速器件,时钟速度和信号上升时间很快。PCB本身尺寸也在逐渐缩小,导致PCB密度增加。元器件和PCB的参数、损耗的影响、电源分配、元器件在PCB上的布局、高速信号的布线等因素,都会引起信号的完整性(SI)问题,导致系统工作不稳定,甚至完全不工作。因此高速设计本身已成为设计过程的重要部分。在千兆网闸的系统设计完成之后,必须仔细考虑其信号的完整性设计问题。

1 设计指导原则

1.1 网闸技术

网络隔离的思路在于:中断直接连接,把协议剥离掉,还原成原始数据,对数据进行检查和扫描,防止恶意代码和病毒,不依赖于操作系统。网络隔离技术具有最高的安全性,因此成为安全市场的黑马,而基于网络隔离技术的产品―网闸,则逐渐成为主流。网闸在OSI七层模型上全面进行隔离。采用三模块结构―两个主机子系统、控制电路和存储介质组成的隔离设备。两个独立主机子系统分别连接安全与非安全网络。保证存储介质与安全网络连通时,断开与非安全网络的连接;与非安全网络连通时,断开与安全网络的连接,通过数据摆渡实现安全的数据交换。网闸从物理层进行网络隔离,消除了数据链路的通信协议,剥离了TCP/IP协议和应用协议,在安全交换后再进行协议的恢复和重建。

本文的网闸系统采用了动态开关技术―基于内存总线的设计。FPGA作为独立控制电路,存储介质为双端口静态存储器,以下简称DPRAM(Dual Port SRAM)。DPRAM每一个端口的接口部分分别与外部、内部主机的内存系统相连,以实现在外部、内部主机两个端口上的开关。两个开关不能同时闭合,原理如图1所示。

1.2信号完整性

1.2.1概述

信号完整性是指信号在电路中以正确的时序和电压做出响应的能力。如果电路中信号能够以要求的时序、持续时间和电压幅度到达IC,则该电路具有较好的信号完整性。反之,当信号不能正常响应时,就出现了信号完整性问题。从广义上讲,信号完整性问题主要表现为5个方面:延迟、反射、串扰、同步切换噪声(SSN)和电磁兼容性(EMC)。

延迟是指信号在PCB的导线上以有限的速度传输,信号从发送端发出到达接收端,其问存在一个传输延迟。信号的延迟会对系统的时序产生影响,在高速数字系统中,传输延迟主要取决于导线的长度和导线周围介质的介电常数。反射是指当PCB上导线(高速数字系统中称为传输线)的特征阻抗与负载阻抗不匹配时,信号到达接收端后有一部分能量将沿着传输线反射回去,使信号波形发生畸变,甚至出现信号的过冲和下冲。信号如果在传输线上来回反射,就会产生振铃和环绕振荡。串扰是指由于PCB上的任何两个器件或导线之间都存在互容(mutualcapacitance)和互感,当一个器件或一根导线上的信号发生变化时,其变化会通过互容和互感影响其他器件或导线。串扰的强度取决于器件及导线的几何尺寸和相互距离。当PCB上的众多数字信号同步进行切换时(如CPU的数据总线、地址总线等),由于电源线和地线上存在阻抗,会产生同步切换噪声,在地线上还会出现地平面反弹噪声(简称地弹)。SSN和地弹的强度取决于集成电路的I/O特性、PCB电源层和地平面层的阻抗以及高速器件在PCB上的布局和布线方式。另外,同其他的电子设备一样,PCB也有电磁兼容性问题,其产生也主要与PCB的布局和布线方式有关。

1.2.2千兆系统的SI

千兆系统有众多高速信号,信号完整性更加突出。许多低速设备设计中无需考虑的方面,现在都很可能成为系统性能下降甚至崩溃的原因。下面着重讨论千兆系统PCB信号完整性设计应重点考虑的一些方面。

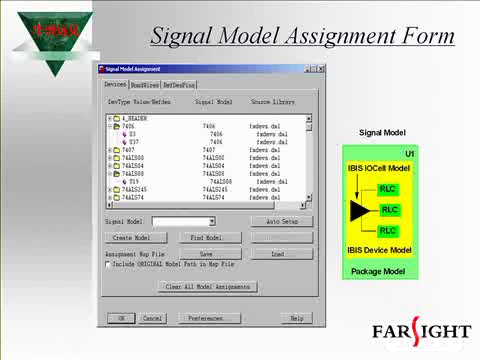

(l)高速器件模型

能够进行仿真的前提是,芯片的电气行为和互连信号线有足够准确的描述。这主要通过对芯片的缓冲器和走线建模实现。对芯片的缓冲器建模主要通过SCICE网表描述和通过IBIS模型描述两种方式。SPICE网表的仿真非常精确,因为它是对缓冲器结构一个几乎完整的描述;但从另外一方面看,这样也会造成芯片设计细节的泄漏以及由于仿真涉及的大量计算造成不可容忍的缓慢速度。IBIS模型是行为级模型,只是采用I/V和V/t表的形式来描述芯片I/0单元和引脚的特性,不涉及内部细节,拥有较快的仿真速度;同时,IBIS规范是由国际标准组织ANSI/EIA来维护的,对于所有的仿真软件有统一的描述规范,得到了绝大多数仿真软件厂商的支持,因此IBIS模型是当前主要的I/O仿真模型规范。标准元件制造商现在都提供IBIS模型。仿真工具也可以自己建立模型。对于PCB的走线建模主要采用传输线模型,可以由2D、2.5D甚至3D的电磁场解析器来分析。比较熟悉的仿真工具SpecctraQuest中就内嵌了场解析器。

(2)差分信号

差分信号通过一对信号线来传输。一条信号线上传输通常所理解的信号;另一条信号线上则传输一个等值而方向相反的信号。如果一条信号线上的电压高于另一信号线上的电压,就可得到一种逻辑状态;而如果前者低于后者就可得到另外一种逻辑状态。这种信号的优点有:很容易识别小信号;对外部电磁干扰(EMI)是高度免疫的。

(3)电源分配系统

电源系统为信号转换提供稳定的电压参考,为所有的逻辑器件分配电源,是整个系统的驱动部分,地位十分重要。在电源系统中,电源模块有极低的输出阻抗。安装在板上的电路通过电线、电缆或电路板走线连接到电源。这条线称为电源分配线。电源分配线具有相对大一些的电感,增大大多数电源的低输出阻抗。其直流特性可能比较好,但是高频的阻抗将会增大。这些都影响了电源和地之间的阻抗。电容的寄生参数包括一个等效串连电感(ESL)和一个等效串连电阻(ESR)。电容的模型是电容、电感和电阻的串连。在电路板上布放的大旁路电容,与电源并联。在一定频率范围内,此旁路电容提供了电源和地之间的一个低阻抗回路;但是在一些更高的频率下,大旁路电容又会因为其引脚电感(ESL)的值增大而失去效果。此时,可以安放小电容阵列来实现第二级的旁路。N个容值为C、ESR值为R、ESI值为L的小电容并联后,其容值为NC,等效串连电感变为L/N,等效串连电阻变为R/N。平行的电源平面和地平面提供了第三级的旁路电容。这些电容引脚电感和串连电阻值为零,在非常高的频率下可以减少电源和地噪声。电源、布线、大旁路电容、小旁路电容阵列与电源和地平面之间的固有电容,在这些因素的共同作用下,在整个工作频率范围内为每个逻辑器件提供了一个低的电源源端阻抗,组合起来统称为多级电源分配系统(multilayereId powar distribution system)。因此,从板级的角度来看,电源分配系统由电源模块VRM(Voltage Regulator Modtlle)、电源平面和地平面、各种电容组成。它们分别在不同的频率范围内做出响应。电源模块响应的频率范围大约是从直流到lkHz,大的电解电容提供电流并在1 kHz~1 MHz的范围内保持较低阻抗,高频陶瓷电容组成的小电容阵列在1MHz到几百MHz的频率范围内保持较低阻抗,电源和地平面对则在100 MHz以上发挥重要作用,如图2所示。

2 设计方案

2.1 网闸系统设计

2.1.1 内外网接口的实现

考虑到x86架构的安全问题,采用了完全不同于英特尔x86架构的MIPS CPU。由于整个系统的数据交换速度达到千兆,必须要求所选择的处理器具有很高的处理性能。据此选择了PMC-Sierra公司的。RM7065C处理器。它是具有指令预取功能的双发射对称超标量64位处理器,主频600MHz,64位SysAD总线工作频率为100MHz。GT64240是MarvelI公司的北桥芯片。该芯片拥有2个32/64位PCI接口,3个百兆网口,内建有DMA控制器和PCI仲裁器,其内部使用的Crossbar技术能够提供高达100 Gbps的数据吞吐量,同时允许CPU、PCI、LAN、WAN和memoiy间数据的DMA无阻塞传输。Intel 82544GC千兆以太网芯片连接到北桥的PCIO口,数据传输采用DMA方式。82371AB是Intel 南桥芯片,与北桥的PCll口相连,为系统提供IDE接口;同时,通过ISA总线连接I/O芯片,再凭借I/0芯片为系统提供PS/2鼠标键盘接口。SDRAM为系统内存,采用标准168脚SDRAM插槽,工作时钟频率133 MHz,大小为256 Mb。EEPROM使用29C040存放BIOS,大小为4Mb。

2.1.2隔离设备的实现

隔离设备由存储介质和FPGA控制芯片构成。选用的FPGA是Xilinx公司的XC2V40。它是Virtex-II家族中的一员。Virtex-II系列FPGA是Xilinx公司开发的新一代大规模SRAM工艺的主流产品,存储介质使用的双口SRAM采用的是两片IDT公司的IDT70V3579S。采用位扩展方式将32位宽度的数据扩展成64位,以符合SDRAM的64位读写方式(64位数据位,8位校验位)。

MIPS体系架构中,空间地址是统一编址的。北桥负责完成地址映射。北桥的SDRAM控制器的SCS[3:0]片选端对应一定的地址段。当CPU访问内存即这些地址段时,就会使能相应的SDRAM的片选信号。本设计使用L/R_SCS3选中FPGA,从而整个隔离设备开始工作。

利用片选使能双口SRAM,并把双口SRAM挂在SDRAM总线上,把双口SRAM当成SDRAM的一部分,但SDRAM和双口SRAM不是同时选中。当SPU访问到相应地址时就能对双口SRAM进行操作,从而完成数据摆渡的工作。但是,SDRAM操作规范和双口SRAM的操作规范并不相同,并且如果2个CPU同时写同一双口SRAM地址时也会出错,因此FPGA既要完成不同规范之间的协议转换,还要完成对双口SRAM存储资源的统一管理。

为避免可能因为同时写而出现错误,把两片双口SRAM中32K64位的资源以地址形式分成高低两部分。考虑到CPU对Cache每次存取数据的大小是2 KB,为了取得较好的Cache命中率,相应地把双口SRAM资源也分成2 KB大小的段。因为两片双口SRAM共有258KB容量,这样就变成了总共128段,并划分成了高64段和低64段。把高64段作为左端北桥写入部分和右端北桥读出部分,把低64段作为右端北桥写入部分和左端北桥读出部分。FPGA发出高7位地址L/R_SEG_AD[14:8]作为双口SRAM的段地址(选中128段中的某一段),与北桥发出的14位地址L/R_ADD[13:0]中的低8位地址L/R_ADD[7:0](作为段内地址,选中某一段中的某8B)组成DPRAM的15位的完整地址,访问DPRAM。其示意图如图4所示。

2.2信号完整性设计

2.2.1 Sl仿真分析

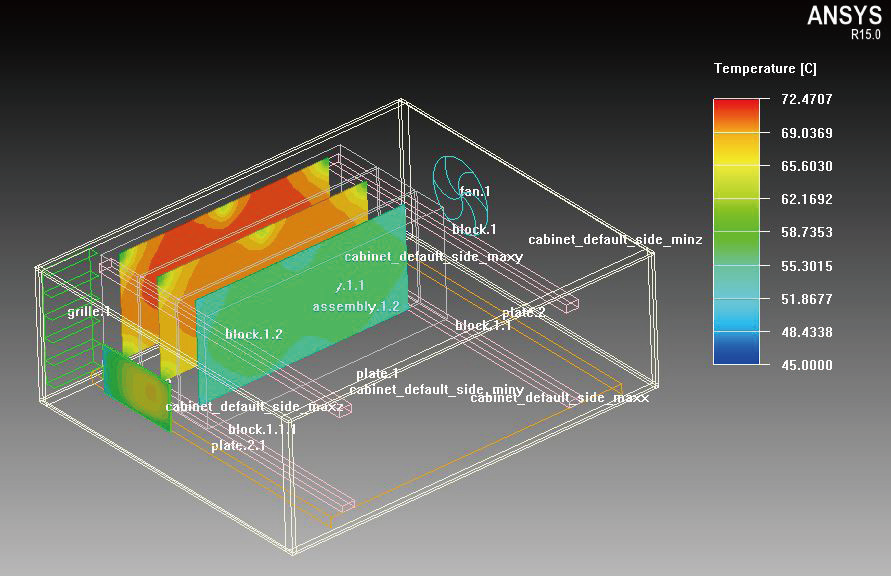

实际设计中,运用Cadence公司的SpeccctraQuest(以下简称SQ)。SQ是一个功能强大并全面支持IBIS模型的仿真工具,它提供图形化的拓扑结构显示(在Sigxplorer中显示,再调入SigWave显示仿真结果的波形),可进行完整的有损传输线SI分析:释放鼠线提取布线前或布线后的互连参数,从而控制驱动能力、阻抗匹配、防止串扰和反射等设计。由于网闸主板中信号数量非常多,对全部信号进行SI分析是不现实的,也是完全没有必要的。这里采取了重点分析的策略,选取的重要信号是左边外部子系统的共用信号L_SD_DP_CLK,它是北桥、两片双口SRAM―IDT公司的70V3579S(采用位扩展方式将32位数据扩展成64位以符合SDRAM读写方式)以及FPGA三者的共同时钟信号,对它进行仿真分析,结果如图6所示。

较粗的一根线是主时钟芯片发出的数据信号L_SD_DP_CLK,另外四根较细的线分别是北桥、FPGA、两片双口SRAM(每片各需要一个)的接收信号波形。无论是接收信号,还是发送信号,波形出现了严重的失真:在高电平和低电平的维持阶段,信号很不平稳;在高电平处有明显的振铃效应;信号上升沿出现了非单调的情况,并且上升沿的切换时间很长;信号的下冲最大接近一900mV,某些信号在下冲幅值比较大时持续时间还比较长,可能会对接收端芯片造成损坏或影响。

针对仿真出现的情况进行分析,注意到离驱动芯片越远,越容易出现超过门限的负过冲,且持续时间更长,幅度更大。同时一个驱动芯片有多个接收芯片,要使驱动芯片尽量处于多个接收芯片的中间位置,保证信号完整性。根据分析结果,对布局进行了调整,为主时钟驱动芯片腾出了空间,相应调整了其他接收芯片的相对位置,并注意调整了源端和负载端的端接电阻值。然后对此信号网络进行了第2次布线前仿真,其仿真波形如图7所示。

图7中,第1次出现的振铃、非单调上升沿、下冲、上升沿切换时间过长等现象都得到了极大的改善;而且,与发送信号波形相比,除了一个接收信号稍微有一些差异以外,其他的接收信号几乎与发送信号波形吻合,说明时延很小,信号完整性得到了保证。仿真结果令人满意,这样的布局也是可取的。前仿真作为对新设计探索性的仿真是成功的。

2.2.2差分信号布线策略

在千兆信号传输中,高速重要信号采用差分信号布线,可以更好地降低串扰、EMI等的影响。在差分线对的布局布线过程中,差分线对中的两条PCB线应完全一致,即确保差分线对中的PCB线具有完全一样的阻抗并且布线的长度也完全一致;同时差分线对的布局布线应尽可能地靠近。差分线用眼图来分析仿真结果。仿真软件设定随机序列码产生眼图,并且可以输入抖动与偏移参数分析其对眼图的影响。

2.2.3电源分配系统解决方案

在千兆系统中,要避免SSN的干扰,保证电源分配系统在带宽范围内具有较低阻抗。一般在低频段,采用去耦电容降低阻抗,高频段主要考虑电源、地平面分布。SPECCTRAQuest可以分析由于封装结构造成的SSN的影响。其中的Power Integrity软件采用频域分析电源分配系统,可以有效分析去耦电容数量与位置以及电源、地平面的影响效果。对EMC,则需要将控制EMC的各项设计规则应用在设计的每一个环节,实现在设计各环节上的规则驱动和控制,设计完成测试验证后又可以形成新的规则应用到新的设计中。

结语

本文讲述了网闸的实现原理,给出一套MIPS千兆网闸的实现方案。该设计为同样采用MIPS IV指令集的国产CPU龙芯2号的推广和应用提供了借鉴。同时提出的千兆系统PCB信号完整性设计方法具有很强的实用意义和先进性,不仅能够有效提高产品设计的性能,而且可以大幅缩短产品开发周期,降低开发成本。

评论