基于单载波调制器中TS流传输的设计和实现

【摘 要】 本文介绍了数字电视地面传输广播中TS流在单载波(ATSC)调制器中的传输,详细说明了ASI接口的转化,论述了TS流速率与调制器净数据率的速率匹配问题,并使用CY7B933、CY7C433和FPGA实现了TS流在调制器中的正常传输,最终给出了硬件设计结果。

【关键词】ATSC; TS; ASI; SPI; 插空包

1 概述

随着数字技术的不断发展,数字电视取代模拟电视已经是必然的趋势。当今世界地面数字电视传输标准主要有美国的ATSC标准,欧洲的DVB-T标准和日本的ISBT-T标准。ATSC标准是基于单载波调制的技术,它具有传输容量大、工作门限低、相同覆盖条件下要求发射功率低、抗脉冲干扰能力强、对调谐器要求低等优点,同时经过大量的测试已经成功应用于实际的数字电视地面广播传输中【1】。由于编码器以传输流(TS)的形式并配以ASI或SPI接口传输到调制器,因此在设计调制器时应该首先考虑接口规范的不同和速率匹配等问题,本文主要是基于ATSC调制器来讨论TS的传输。

2 TS流在调制器中的传输

2.1 调制器结构

图一 调制器中的TS流传输

在无线广播数字电视传输系统中,统一规定以MPEG-2的传输流即TS流(transport stream)形式进行传输,也就是说视音频信息经过编码器的处理形成TS流的标准形式,每个TS包有188个连续的字节,其中位于包头的第一个字节固定为47H。编码器输出接口一般分为两种形式,ASI口(Asynchronous serial interface)和SPI口(Serial Peripheral Interface),前者是一种高速串行数据通讯接口,具有高速、可靠、准确等特性;后者属于一种并行总线接口,易于进行数据处理。但无论采用哪种接口,调制器都需要对其进行速率匹配的处理,因为虽然编码器的输出速率可以固定在4Mbps到20Mbps不等,但实际传送的每个TS包的速率不固定,且TS包之间的间隔也不固定,这对于需要连续处理数据的调制器来说是不允许的。所以设计的调制器可传送的净数据率必须大于编码器的输出速率,并在TS流中适当的插一些空包(符合MPEG-2标准),以获得连续的码流。

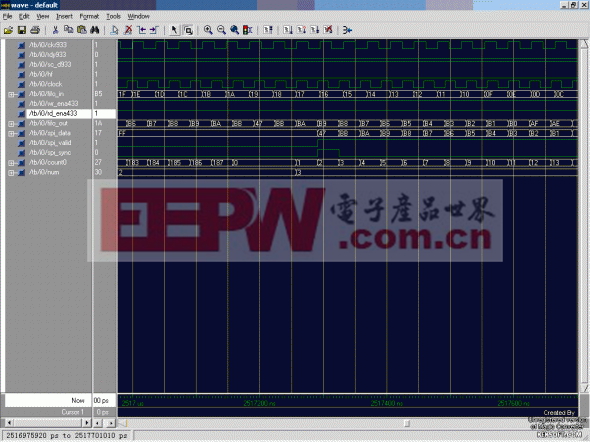

图一表示了TS流在调制器中的传输过程,其中片内FIFO即用于上诉的速率匹配,接下来TS流需要经过扰码,外编码和交织等模块最后组帧输出用于调制,中间的交织器由于使用RAM,可以间接起到由于组帧时插入同步信息的数据缓冲作用,同时组帧输出的数据使能反馈回FIFO要新的TS流,周而复始。本文设计的这种调制器结构具有修改性强的特点,原因在于一旦帧场结构有所变化,只需要修改相应的数据使能的产生,而与前级处理无关,有利于TS流在调制器中的连续传输。

2.2 TS流传输中ASI口的转化

图二 ASI口转化的实现框图

ASI是一种固定波特率的异步串行接口,其突出特点是:速度快,固定波特率,准确。来自不同数据信源的波特率可能是不同的,通过在这些数据中间插入同步字而使用固定波特率(270M)传输【2】。此外,其数据还经过8Bit到10Bit编码,在传输数据的空余段插入同步字,具有较强的抗扰、错误检测和再同步能力。

为了得到并行传输的TS流数据,需要对ASI口进行转化,如上图所示,CYPRESS公司的CY7B933和CY7C433配合使用,可以很好的解决这个问题,他们的主要引脚如下:

CKR:CY7B933的恢复时钟,一般为27M,配合数据的输出;

RDY:数据输出准备,低有效,表示数据已经被接收准备传送,属于正常;

SC/D:特殊字符/数据选择,低有效,表示Q0~7为有效数据;

Q0~7:CY7B933并行数据输出;

Read_ena:FIFO的读使能信号,低有效;

Write_ena:FIFO的写使能信号,低有效;

HF:FIFO的半满信号,低有效;

可将RDY信号和SC/D信号组合产生FIFO的写信号,将有效的数据写入FIFO,FPGA通过判断半满信号HF连续地从FIFO中读取一个TS包长度的数据。但只得到TS数据流是不够的,必须加入一些指示线证明数据的正确性,相似于SPI口的标准形式,产生sync用于指示包头位置,valid用于指示一个数据包的有效性,并配合FPGA本地的时钟clk(一般30M),方便后级处理。搜索包头的流程图如下:

图三 搜索TS流包头流程图

2.3

2.3

TS流传输中插空包处理

经过接口处理的TS流虽然包括sync和valid的信号,但是速率仍然和调制器的其他模块有冲突,尤其数据流的连续性由组帧时的使能控制,所以仍然必须对TS流进行插空包的处理,且使输出符合帧结构特点,这也是本文设计调制器的关键。

这里又得需要一个FIFO,但由于编码器输出速率和调制器净数据率往往相差不大,可以考虑使用片内FIFO,在对FIFO输出的数据进行判断时,需要用到sync指示线,为了方便处理,将FIFO设为9位位宽(sync、data),深度设为4K。相似于上述的ASI转化,读FIFO时也需要判断半满信号HF,不同的是要确保写入FIFO的第一个数据是包头47H,这样可以保证以后每次读取一个完整的TS包。当HF无效时插入空包,空包的具体格式为:

图四 空包数据结构

但是值得注意的是由于ATSC标准中的帧长不一定是TS包的整数倍,也就是说读FIFO或插空包时可能不会是一个完整的包,为此需要新增状态机FIFO_stop,记录停止的位置(保持188计数器的值),以便使能再次有效的时候继续处理上回的数据,具体状态机的实现如下图所示:

图五 插空包的状态机实现

3.硬件实验结果

(见TIF图像附件)图六:ASI转化仿真示意图

(见TIF图像附件)图七 插空包过程的仿真示意图

本文的硬件设计采用ATERA公司的APEX系列芯片【3】,仿真工具为MENTOR公司的ModelSim软件,经过仿真和硬件调试,工作正常。

图六所示的仿真结果中采用片内FIFO模仿CY7C433,而且经过硬件调试,ASI转换模块良好,搜索包头47H迅速,达到系统的速率要求。插空包模块的仿真波形(图七)更加准确的解释了状态机之间的跳转,其中state的数值表示如下:

0:系统复位;1:读FIFO工作;2:插入空包;3:读FIFO或插空包暂停。

可见系统起始状态FIFO未达到半满所以插入了2个空包,其后开始读FIFO,由于读到一半,帧使能信号gen_ena_bit为低,进入状态3,待使能信号再次为高,接着上回的位置继续读取FIFO,位置计数器rd_cnt开始计数。

4.结束语

本文设计的调制器TS流传输方案,利用CYPRESS公司的CY7B933和CY7C433的配合,通过FPGA作为逻辑控制,解决了TS流传输中的接口不统一和速率不匹配等问题,并通过了硬件的仿真和调试,可应用于许多现有的数字电视地面广播传输系统中,如美国的ATSC标准和中国的ADTB_T,具有很强的实用性。而且就ASI转化部分而言也可以应用于以DVB_T为代表的多载波传输系统,有一定的通用性。

参考文献

【1】 The Grand, “The U.S. HDTV standard,” IEEE Spectrum, April, 1995, pp. 36-45.

【2】 关东亮,余松煜. 一种新的高速ASI的设计与实现. 数据采集与处理, 2001(12):490-493.

【3】 夏宇闻. 从算法设计到硬线逻辑的实现. 北京:高等教育出版社,2001. 122-159.

评论