基于Virtuoso平台的单片射频收发系统电路设计

摘要:本文基于对Cadance Virtuoso 平台的研究,结合单片射频收发芯片的设计实践,讨论了利用Virtuoso 完成的自顶向下、从系统到模块、从前端到后端的整个设计流程,最终实现了一个完整的射频芯片。

关键词:Cadence Virtuoso;自顶向下设计流程;单片射频收发芯片

引言

在当前通信市场的带动下,通信技术飞速向前发展,手持无线通信终端成为其中的热门应用之一。因此,单片集成的射频收发系统正受到越来越广泛的关注。典型的射频收发系统包括低噪声放大器(LNA)、混频器(Mixer)、滤波器、可变增益放大器,以及提供本振所需的频率综合器等单元模块,如图1 所示。对于工作在射频环境的电路系统,如2.4G 或5G 的WLAN 应用,系统中要包含射频前端的小信号噪声敏感电路、对基带低频大信号有高线性度要求的模块、发射端大电流的PA 模块、锁相环频率综合器中的数字块,以及非线性特性的VCO等各具特点的电路。众多的电路单元及其丰富的特点必然要求在这种系统的设计过程中有一个功能丰富且强大的设计平台。在综合比较后,本文选定了Cadence Virtuoso 全定制IC 设计工具。

图1 典型的射频收发系统

Virtuoso 是Cadence 公司推出的用于模拟/数字混合电路仿真和射频电路仿真的专业软件。基于此平台,Cadence 公司还开发了面向射频设计的新技术,包括射频提取技术、针对无线芯片设计的两个新设计流程。不仅如此,目前的Virtuoso 已经整合了来自合作伙伴安捷伦、CoWare、Helic 和Mathworks 等公司的技术,射频设计能力大为增强。使用该项新技术,可以减少设计反复,并缩短产品上市时间。其AMS 工具可以实现自顶向下、数/模混合的电路设计;Composer 工具可以方便地进行电路设计的输入和管理;Spectre/SpectreRF 仿真器精度高,适合不同特点的电路设计;Layout工具包含了布局、交叉参考、布线、版图验证、参数提取等功能;此外,Virtuoso能进行可靠的后仿真和成品率控制。

基于Virtuoso 的行为仿真和系统规划

射频收发系统的设计最终能否成功,以及模块指标分配是否合理可行,都有赖于具体电路设计之前对系统的行为建模和计算,即所谓的行为仿真。这也是自顶向下设计模式的关键一步。Cadence 内置的Verilog-A 和VHDL仿真器,以及混合输入模式的仿真方法提供了这种可能性。而且,Cadence 软件免费提供了大量的行为模型供选择使用,对于射频系统设计,所要做的就是调用并设定各个模块预期的指标要求,通过仿真很快就能得到系统的行为特征。根据要求可以方便地修改各个模块的指标重新仿真,直到系统的行为满足要求为止。以接收机为例,接收系统如图2所示。每个模块的指标设定非常具体,如输入输出阻抗、增益、隔离度、噪声系数NF、线性度IP3、直流偏移IP2等。仿真完成后,每个模块的指标分配任务也同时完成。

图2 基于Verilog-A 的接收系统行为仿真

每个模块用具体电路实现后可以逐一取代相应的设计模块,进行系统仿真,可以看出每个模块是否满足系统的需要,进而评估每个实际模块对系统性能的影响。

基于Virtuoso Spectre/SpectreRF 的电路模块仿真设计

基于上述的行为仿真结果和指标分配结果,可以划分系统模块设计任务,对每个单元块分别进行设计仿真。

LNA

LNA 是射频接收机最前端的一个有源部件,它决定了系统的噪声性能。对它的要求主要是具有尽量低的NF 和足够的功率增益、好的输入匹配,其次是高线性度和隔离度。其电路如图3所示。利用Spectre 的SP 分析或SpectreRF 的PSS+Pnoise 分析都可以进行NF分析。还可以利用NFmin 的结果来挑选晶体管的尺寸,以使最优源阻抗满足最小的噪声要求。

图3 LNA 电路原理图

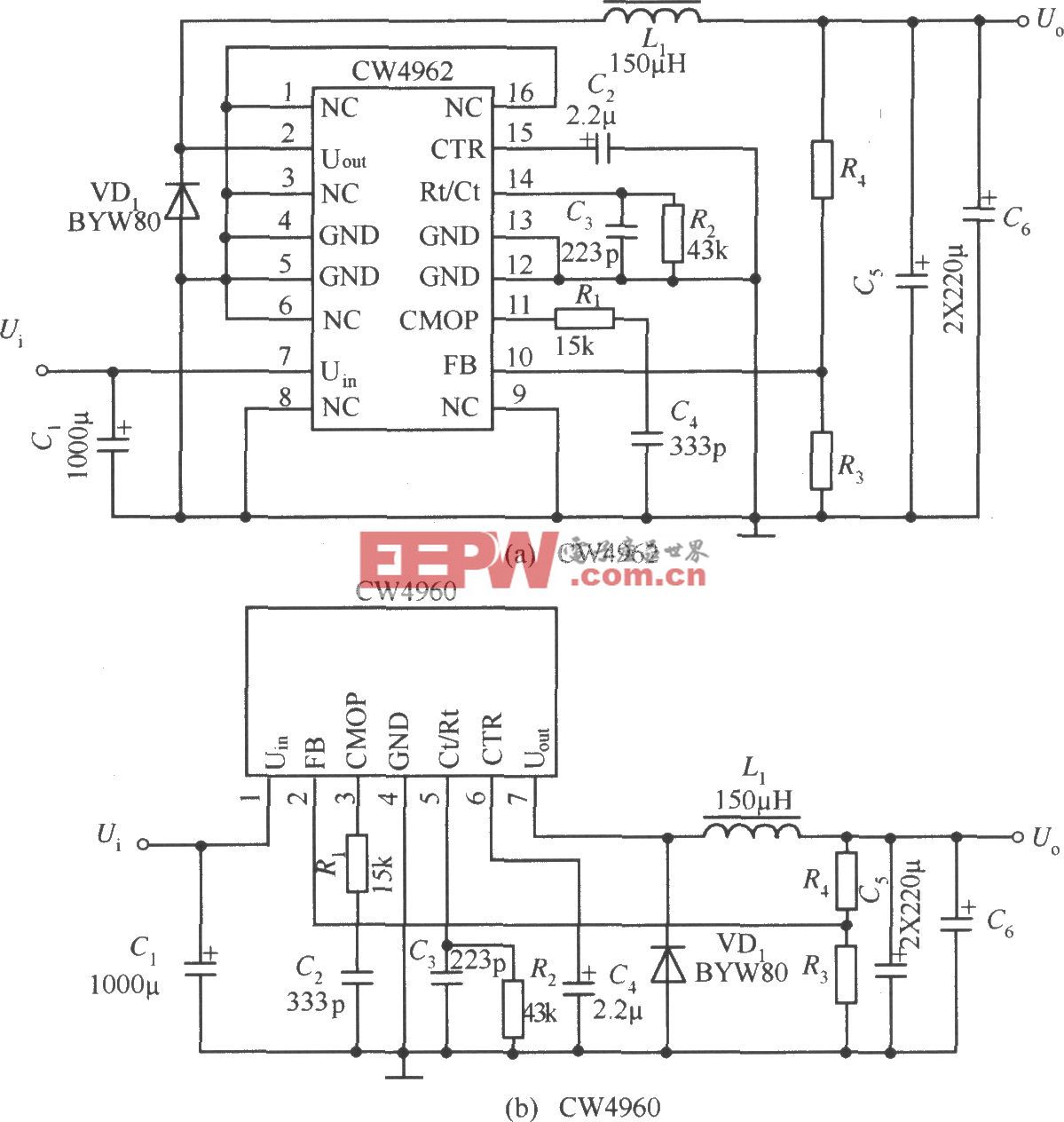

Mixer

混频器是收发机的核心,由于完成的是变频工作,其主要仿真方法需采用SpectreRF 仿真器。混频器的增益、NF 等与输入输出有关,但输入和输出工作在不同的频段上,往往要在PSS 分析的基础上进行其它分析才能得到正确结果,如PSP、Pnoise、PAC 等。混频器的结构是典型双平衡吉尔伯特。

VGA

基带VGA 由于频率低、增益大,因此对噪声要求不高,主要是对线性度、增益等指标有较高的要求,SpectreRF 的PSS 扫描可以方便地对模块的输入进行扫描并自动对扫描曲线作延长,直接标示出线性度P1dB 和IIP3 的交点位置及数值大小,非常方便直观。这种方法与传统的two tone 测试相比更加灵活高效。VGA 在不同增益状态下的IIP3 指标的仿真只需把控制写成变量,在ADE 环境中进行扫描变量的值即可完成。所得的结果可以方便地进行比较分析。通过调整可以获得理想的VGA 电路。甚至可以把ADE下的各种设置保存成ocean 的脚本文件,利用脚本的自动运行,只要事先安排好各种仿真任务,Cadence就能自动完成各项仿真并保存数据结果。对数据进行比较分析后能获悉电路的性能,以此为指导逐步改进,便可获得一个满足系统需要的电路模块。

PLL 模块

PLL 各模块的仿真是一个比较有挑战性的任务,PLL 本身是一个数字/模拟混合的模块,但是一般都用模拟的方式设计各个模块。PLL 的仿真包含了上百项指标的测试工作,这些仿真要用到几乎所有Spectre 和SpectreRF 的仿真工具。以其中VCO 和CP 的仿真为例,VCO非线性的工作特点决定了它的噪声计算不能以小信号的方式进行,采用PSS+Pnoise的方式则可以准确地仿真VCO 的相位噪声性能。通过扫描可以得到VCO 的频率调谐增益Kvco。

电荷泵输出电流特性是衡量CP 性能的常用曲线,CP 决定了PLL 环路的增益和带内噪声性能。通过扫描也可以容易地得到CP 在不同状态下电流源的恒流和匹配特性。

以上所述是射频接收机几个典型单元模块的电路设计仿真过程。系统各个单元块的仿真是可以同时展开的,完成的模块可以随时代入行为系统来验证设计结果。经过若干次反复修改与验证,最终可以得到符合要求的接收系统。

温度分析

要保证最终系统设计的可靠性和成品率,很关键的一步是在各个单元块的设计中进行温度、极端情况等分析。这些功能可以在Cadence Virtuoso中通过设置不同的仿真温度、通过仿真模型的Corner 设置,以及直接使用其提供的MonteCarlo 仿真工具来进行。

图4 系统电路图 图5 系统的电路测试设置

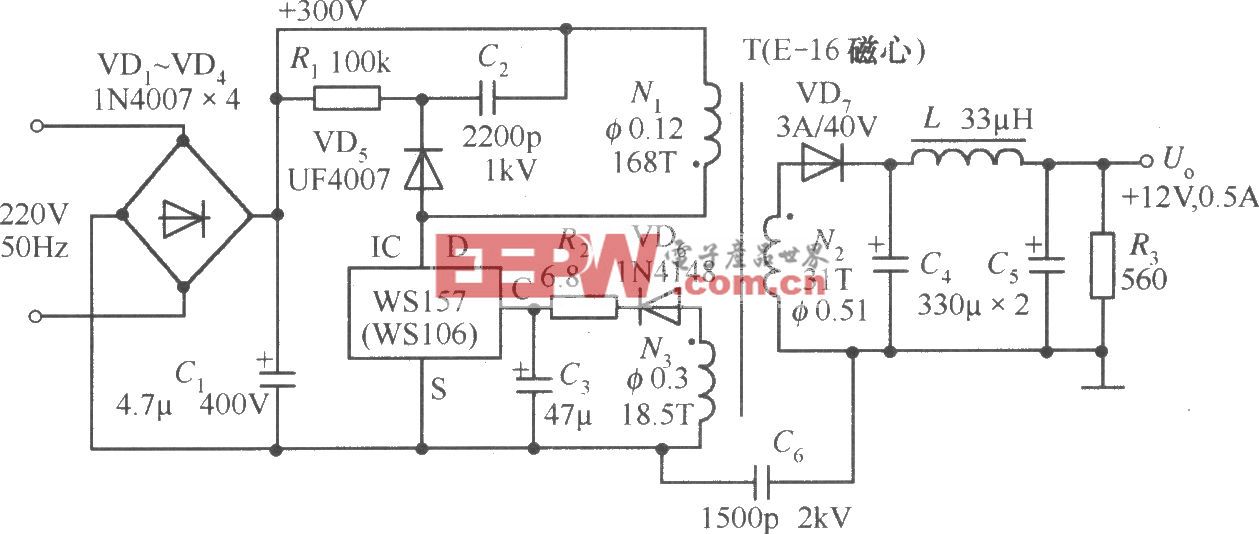

射频收发系统的整体电路仿真

各个模块电路分别设计验证完成以后,就可以把所有模块连成系统,并加上PAD、ESD 等构成一个完整的芯片系统,如图4所示。对这个系统加上激励进行仿真测试,如图5所示,可以对整个系统电路进行仿真。如果仿真计算所用的硬件资源足够大,可以直接对系统进行tran、SP、PSS,以及PSP、Pnoise、PAC 等分析,获得整个芯片的性能。如果资源不足,则可以考虑对系统按功能进行分组、分块仿真。由于分出的块之间相对独立,因此整体系统的特性与分块仿真差别不大。

版图设计与后仿真

在各模块的设计指标满足自身及系统要求的基础上可以开始各个模块的版图设计,如图6所示。首先利用Layout-XL 的元件调入功能可以直接由原理图调入版图元件,进行各个模块的粗略布局,主要是安排与其它模块的连接端口以及一些重要元件的预布局。然后从系统上将所有模块的预布局调入进行整体布局考虑。利用Virtuoso Layout 工具所具有的层次化管理和操作的特性,可以对每个模块的安放及其与其它模块的衔接进行系统考虑。

图6 单片射频收发芯片版图设计

系统布局以后,将边界条件分配给每个模块。在模块单独的布局过程中要遵守其边界约定。版图进行到一定阶段后,即可以调入到系统版图中来检查,随时作必要的调整以满足每个模块的具体情况。

具体版图绘制过程中可以充分利用Virtuoso 版图工具的强大功能,比如充分发挥快捷键功能可以使版图设计流畅高效;利用Layout-XL 的交叉参考可以随时发现错误的连线或因疏忽造成的短路;利用DRD 的实时规则检查可以避免绝大多数违反设计规则的布图。

版图的规则检查可以采用Virtuoso 的Diva 工具, DRC、LVS、Extract 等工作都可以在其友好的界面下完成。对于射频电路版图元件数规模不大的特点,利用Diva 完成绝大部分工作是很合适的。如果想进一步提高版图提取和后仿真的精确度,可以考虑采用Assura 工具来进行。

结语

本文详细讨论了基于Cadence Virtuoso 设计平台的单片射频收发集成电路的设计过程。讨论了利用Virtuoso 工具完成的自顶向下、从系统到模块、从前端都后端的整个设计步骤,直到实现一个完整的射频芯片。可以看出,Virtuoso 平台工具在IC 设计的各个阶段所发挥的重要作用。

文中所述的单片射频芯片设计中所采用的Virtuoso工具只是Virtuoso 家族中最常用的几个工具,依靠他们的强大功能足以完成复杂的射频系统设计,是性价比较高的一种解决方案。如果再结合Virtuoso 的AMS、UltraSim、VoltageStorm、ElectronStorm等工具,将会使设计效率更高,设计更精确。

参考文献

1. R. Telichevesky, K. Kundert, and J. White.Receiver characterization using periodic small-signal analysis.1996

2. J. McDonald, R. Maini, L. Spangler, and H. Weed.Response surface methodology: a modeling tool for integrated circuit designers. Solid-State Circuits, IEEE Journal of, vol. 24, pp. 469-473, 1989

3. H. Samueli.Broadband communications ICs: enabling high-bandwidth connectivity in the home and office.presented at Solid-State Circuits Conference, 1999. Digest of Technical Papers. ISSCC. 1999 IEEE International, 1999

4. R. G. Meyer and W. D. Mack.A DC to 1-GHz differential monolithic variable-gain Amplifier. Solid-State Circuits, IEEE Journal of, vol. 26, pp. 1673-1680, 1991

5. H. Darabi, J. Chiu, S. Khorram, K. Hea Joung, Z. Zhimin, M. Hung, Chien, B. Ibrahim, E. Geronaga, L. H. Tran, and A. Rofougaran.A dual-mode 802.11b/bluetooth radio in 0.35-/spl mu/m CMOS. Solid-State Circuits, IEEE Journal of, vol. 40, pp. 698-706, 2005

评论