基于cPCI总线的高速数据光纤传输系统的实现

摘要:介绍一种基于cPCI总线的点到点高速数据光纤传输系统,提出了用现场可编程大规模集成逻辑器件取代分立元件完成接口卡设计及力求达到更高的传输速率的思想,并实际设计实现了这种想法。着重介绍了系统的硬件结构设计和软件功能实现,给出了选用的主要芯片的型号。实验证明该系统工作稳定,达到了设计指标要求。

关键字:cPCI总线,FPGA,数据传输,PCI9056

1.引言

高速数据传输系统设计的关键是主机接口卡的设计与实现。传统的做法是采用分立元件,由若干个模块构成。大多数的设计都类似于如下结构[1]:接口的主要功能模块包括光电信号转换接口(O/E和E/O)、串行化和解串行化模块(TX和RX)、数据缓存F I F O 、c PCI 控制器和可编程逻辑模块(FPGA或CPLD)或DSP。各模块中O/E和E/O 实现光纤通道串行光信号和串行电信号之间的相互转换。TX和RX 实现将串行电信号和并行电信号的相互转换功能。F I F O 主要实现光纤通道和cPCI 之间信号的缓冲。cPCI 控制器实现FIFO 输出的信号与32 位标准cPCI 信号的转换。FPGA或CPLD 负责各模块之间的时序协调和传输控制。分析以上方案可见,各模块功能都是由分立芯片完成的。这样各芯片间的互连势必会影响传输速率,也将使PCB板的布局布线变得复杂,使传输延时增大,进一步降低传输速率。而随着FPGA(Field Programmable Gate Array)技术的不断发展,其容量、功能、可靠性以及响应速度都在不断的提高。用一片FPGA完全可以实现计算机与光纤通道之间的数据传输与处理。鉴于此,本论文的设计将用一片FPGA来实现串行信号与并行信号的相互转换、数据缓冲以及时序协调和传输控制等以前用分立元件实现的功能。

2.系统原理及实现

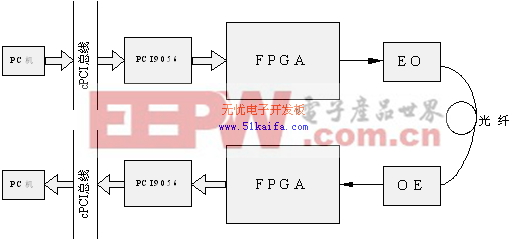

本系统由两台PC机、两块接口卡及一根光纤组成。系统设计关键是基于cPCI总线的接口卡。接口卡采用标准的3U板设计,由总线控制器芯片、可编程逻辑控制器、光电转换驱动器等组成。其结构框图如下图所示。

图1 系统原理图

本系统设计的目的是应用于雷达数据的传输,主要解决点对点的数据传输问题。为了高速、可靠的传输雷达信号,决定采用光纤作为传输媒介,充分利用光纤传输损耗小、抗干扰能力强、传输速率高等优点。其工作流程是这样的:发送端PC机通过cPCI接口将要发送的数据送入FPGA,FPGA对数据信号进行驱动并实现数据缓冲、并串转换等所必需的信号处理过程后形成串行信号,串行电信号经电光转换器转换成串行光信号送入光纤进行传输。在接收端,经光电转换器将光信号转换成串行电信号送入FPGA,FPGA对数据信号进行驱动并实现串并转换、数据缓冲等所必需的信号处理过程,然后通过cPCI接口进入PC机进行存储以待分析处理。设计主要分为硬件设计和软件设计两部分。

一、硬件设计部分

笼统来说,本设计主要是要完成主机接口的实现。主机接口是实现高速数据传输和数据存储的一个关键环节。主要完成高速数据流的信号转换,实现数据在主机上的存储,同时减少CPU对存储过程的干预。CompactPCI简称cPCI,是国际PICMG协会于1994年提出来的一种总线接口标准。它的出现解决了多年来电信系统工程师与设备制造商面临的棘手问题:将VME密集坚固的封装和大型设备的极佳冷却效果以及PC廉价的易采用具有最新处理能力的芯片结合在一起,既保证99.999%的高可靠度,又降低硬件和软件的开发成本。因此希望通过cPCI总线利用DMA方式完成数据的传输与存储。由图1知,接口的主要功能模块包括电光(光电)信号转换模块、可编成逻辑模块FPGA和cPCI总线接口模块。接口各模块中,O/E和E/O实现光信号与电信号的相互转换。FPGA实现几乎所有的信号处理工作,比如实现数据的串行、并行转换与最终通过光纤进行数据传输;实现FIFO功能进行信号缓冲,在高速数据传输中缓存是很重要的,它协调了数据发送端和接收端之间的数据传输速度,防止由于数据流速度的波动导致传输的失败;实现各模块之间的时序协调和传输控制等。cPCI总线接口卡实现FPGA输出的信号与32位标准cPCI信号的转换,通过DMA方式实现cPCI总线到主机的数据存储。主要的研究与设计重点在cPCI总线接口模块、可编程逻辑模块FPGA和光电转换模块。

(1)cPCI总线接口模块

目前,cPCI总线接口的设计与PCI接口的设计一样,一般采用两种方案,即可编程逻辑器件和专用总线接口器件。可编程逻辑器件是根据PCI协议在FPGA或CPLD中实现PCI总线接口控制器,但是由于PCI协议的复杂性,使得开发难度大,周期长,而且很难在短期内达到系统稳定,这种方法比较适合于大批量生产的情况。对于一般的开发者来说,大都采用现成的PCI接口器件。这类专用接口器件具有较低的成本和通用性,能够优化数据传输,提供配置空间,具备用于猝发传输功能的片内FIFO等,是一种省时省力的方案。这类专用芯片有很多,如PLX公司的PCI总线目标接口器件PCI9052、PCI9054,PCI9056,AMCC公司的S5933等。由于cPCI总线的时钟频率是66MHz,数据宽度为32位,故本设计中选用PLX公司的专业总线接口芯片PCI9056作为总线接口控制器,它符合PCI2.2规范,是32位、66MHz的PCI总线主控I/O加速器,适用于通用的32位、66MHz的局部总线设计,局部总线猝发速度可达264MB/s,支持DMA通道,FIFO缓冲区大,是一款性价比比较高的芯片。它的本地总线可为三种模式:M模式,C模式和J模式,可利用模式选择引脚加以选择。本设计选用C模式,即32位的地址/数据总线非复用。

(2)可编程逻辑模块FPGA。

FPGA选用了altera公司Stratix GX系列的EP1SGX10CF672[2]。Stratix GX器件系列是Altera第二代基于收发器的FPGA系列,为需要高达3.125Gbps数据率的应用提供了一条低风险的实现方式。Stratix GX千兆位收发器功能块是嵌入式收发器功能块,它具有四个全双工通道,使用时钟数据恢复(CDR),传输速率高达3.125Gbps。每个通道具有实现数据恢复/传送、串行/解串、解码/编码和同步处理等不同阶段的专用电路。同可编程逻辑结构的无缝接口确保了可靠的数据传输、最大数据吞吐量和简化的时序分析。它兼容光纤通道、串行Rapid I/O等接口协议,集成8b/10b编解码器。本次设计主要使用了其8b/10b编解码模块及光纤通道协议。另外,这款芯片内部含有PLL,且其内部FIFO缓冲区比较大。正是由于该系列芯片功能、容量以及响应速度的大幅度提升,使得一片芯片完成多个分立芯片的功能成为可能,进而提高系统的数据传输速率。

(3)光电转换模块

光电转换驱动器选用了Infineon公司的V23818-M305-L57。这款芯片数据速率高达2.215GBd,兼容光纤通道协议,具有良好的EMI性能。由于该芯片差分输出信号的电平是PECL或LVPECL的,而后面FPGA的高速串行收发器的差分接收信号电平是PCML的,两种接口标准的共模电压不同,所以要采用AC耦合电路来完成两种电平的转换。耦合电容的选择既不能太大也不能太小。如果太大,将严重减缓信号的传输速度,且由于充放电时间过长,对快速变化信号的响应将变得很坏;如果太小,将改变线路的阻抗特性,增大衰减。综合考虑这两种要求,耦合电容的容值在0.01µF比较适当。外部DC偏置电路可以省去,因为Stratix GX器件的高速收发器输入管脚内置的有DC偏置电路,所以所需要的共模电压会在器件内部产生。

二、软件设计部分

接口卡的软件设计主要包括两个部分,一个是FPGA控制程序的编写,一个是板卡驱动程序的编写。以下本文主要就接收端FPGA控制程序的编写加以详细论述。正如前面所述,FPGA主要完成时序协调和传输控制,以及数据流的串并转换和缓存。整个系统的控制采用有限状态机[3]。其状态转换图如下:

图2 接收状态转换图

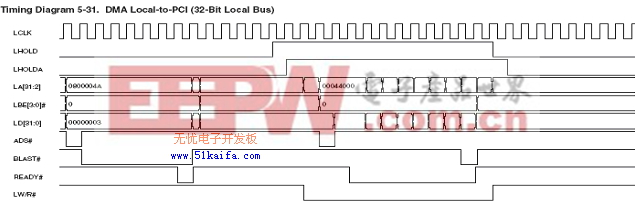

状态机的状态转换以及各个状态下信号的处理完全依据PCI9056的Local端到PCI端的DMA传输时序图。其时序图如下图所示:

转换流程分为3个状态:idle ,prel,dma_read。idle为空闲状态,上电复位后首先进入此状态,在此期间总线无任何操作,只是不断检测ADS#信号,一旦检测到这个信号有效,就进入下一个状态。prel是一过渡状态。根据PCI9056的DMA传输时序图可知,每次一个新的总线接入有效(即ADS#有效)后的第一个数据会持续两个时钟周期(其后的数据持续一个时钟周期),其中,第一个时钟周期并不采集数据,而只是使从设备准备好信号(即READY#)有效,第二个时钟周期才开始采集第一个数据。所以,此过渡状态主要是使READY#信号在采集数据前一个周期有效。dma_read状态期间执行从局部总线到cPCI总线的DMA操作,在每次时钟的上升沿采集数据,直到突发长度内的最后一个数据,BLAST#信号有效,下一个时钟周期,状态机又回到空闲状态,等待下一次传输的开始。对数据的处理是按照数据的流向逐步完成的[4][5]。首先经过OE转换的串行数据进入FPGA,经由FPGA内部的串行高速收发通道完成解码及第一步的串并转换,这时由1bit串行数据变为8bits并行数据;其次由于cPCI局部总线数据线宽度为32位,所以第二步的串并转换要完成8bits数据到32bits数据的转换。其过程是,用4个8bits的D触发器来连续锁存输入的8bits的数据,再用一个32bits的D触发器来同时锁存4个8bits的数据以形成32bits宽的数据输出;最后为了对数据进行缓冲,完成数据速率的转换,将数据存入一32位宽异步FIFO。该异步FIFO的写时钟是从串行数据提取出的随路时钟,读时钟是与总线控制器PCI9056的局部时钟同频的由板上提供的外部66M时钟。

3.总结

本文作者的创新点在于用一块高性能FPGA取代了传统上采用分立元件设计高速传输系统的方法,从而简化了电路设计,减少了元器件间的互连,不但节省了板卡的面积,而且极大的提高了传输速率。该课题基于实验室承担的项目,主要用于雷达数据的传输。设计指标要求采样点数为16384,脉冲重复频率(PRF)6K以上。基于此指标要求并行数据采样时钟频率应不低于50MHz,这样传输速率理论上可以高达200MB/s以上。实验证明该系统的软硬件设计是成功的。该点到点高速光纤数据传输系统不但适用于雷达数据的传输,同时在高速数据采集、远程控制等方面也具有广阔的应用前景。

参考文献:

1. 宋克柱,王砚方,“适用作远程实时数据采集平台的光纤通讯系统”, 数据采集与处理,第16卷第2期2001年6月

2. sgx_handbook

3. 杨进,魏轶伟,何宁,熊剑平,贾惠波,“基于光纤通道的高速数据传输系统主机接口设计”,计算机工程与应用,2002年第22期

4. GE ZHOU,YIMO ZHANG, WEI LIU, “Optical Fiber Interconnection for the Scalable Parallel Computing System”, PROCEEDINGS OF THE IEEE,VOL.88,NO.6,JUNE 2000

5.刘小俊,宋仲康,“基于VHDL语言的全双工异步接收发送器电路设计”,《微计算机信息》(测控自动化),2005年第21卷第1期

评论