便携式RFID射频识别读写器的设计与实现

射频识别(RFlD)技术是一种非接触式的自动识别技术,其基本原理是利用射频信号及其空间耦合和传输特性,实现对静止或移动物体的自动识别。一个射频识别系统一般包括射频标签、读写器以及主机等几个部分。目前国内应用于超高频的RFID读写器较少,而且整机价格昂贵、体积庞大、需外接天线或天线阵列、不便于携带且多不能单机工作。本设计的目的在于以尽可能低的硬件成本实现一种基于ISO/IEC18000―6B标准的便携式RFID读写器,并可通过软件升级后支持其他标准或多标准。

本文引用地址:http://www.amcfsurvey.com/article/158176.htm1、理论分析

RFID系统工作时,首先由读写器发射一个特定的一步的处理。询问信号,当射频标签感应到这个信号后,就会给出相2读写器硬件设计应的应答信号;读写器接收这个应答信号并对其进行处理,返回给外部主机或进行相应操作。

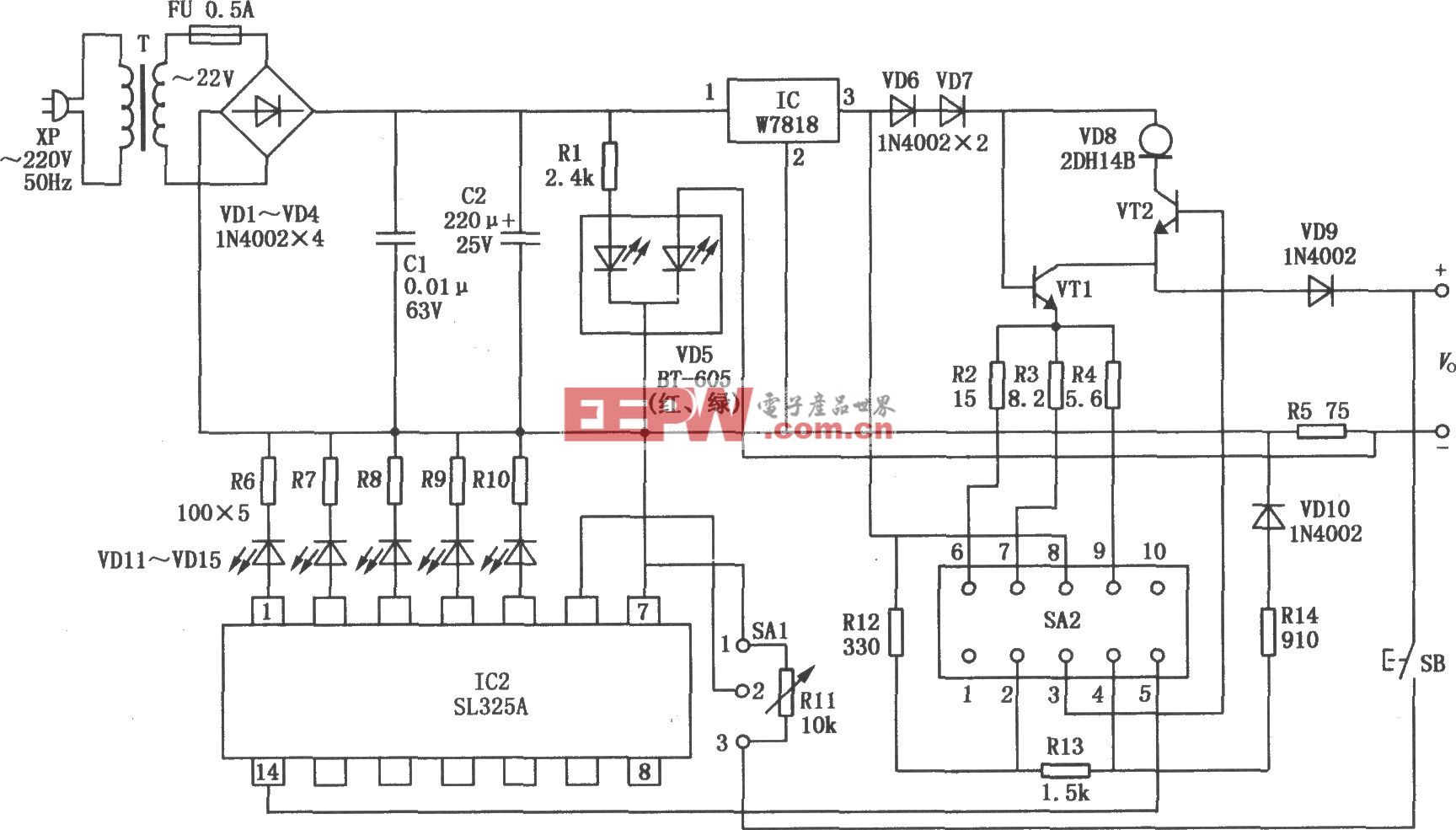

本文所实现的读写器包含射频收发模块和数字基带处理模块,其中射频收发模块又包括射频发射机和射频接收机两部分,总体结构如图1所示。系统在工作时首先由数字基带处理模块产生需要向射频标签发送的询问信号,然后由射频发射机将这个信号转换成为射频信号发射出去。

射频标签接收到这个信号后,会给出相应的应答信号,回波信号。这个回波信号将由射频接收机接收并进行处理,转换成为数字信号后送给数字基带模块进行进一步处理。

2、读写器硬件设计

如前所述,本读写器的硬件主要包括射频收发机模理,返回给外部主机或进行相应操作。块和数字基带处理模块,其中射频收发机模块包括射频发射机和射频接收机,总体结构如图1所示。在系统结构的选择上,本读写器以降低成本为主要目标,射频发射机和射频接收机采用了零中频结构,在很大程度上减少了所需的器件;数字基带处理模块采用了以单片机为主的结构,而没有采用高速的DSP,也节省了一定的成本。

2.1射频发射机

发射机电路主要包括晶体振荡器、频率综合器、功分器、ASK调制器、功率放大器(PA)以及发射天线等。

本设计中,频率综合器采用了集成芯片S14133,这是一款可编程的锁相环芯片,可以通过数字编程控制其输出频率。正是通过这一性能,实现了系统在860MHz一960MHz的频率范围内的跳频操作,从而避免频带内其他信号的干扰。由S14133输出的射频载波经过一个功分器后,一路送往接收机作为本地振荡信号LO,另一路则送至ASK调制器。这里的ASK调制器采用了一款结构非常简单的芯片HMCl95,它可以简化为一个高速开关,由需要发送的数字信号控制其通断,以此完成对载波的调制。经调制的载波由功率放大器放大,最后送至天线发射出去。

鉴于实际工作的需要,这里并没有采用高性能的功率放大器,而是采用了一个价格低廉的缓冲放大器芯片AG503,其输出功率最高可达17dBm,即O.05W。发射天线也采用了极为简单的PCB印制偶极子天线,无需外接。此时读写器的工作距离可达80cm。由于载波在近距离的自由空间的衰减与传播距离的平方近似于成正比,故可以计算当发射机的等效发射功率(EIRP)达到36dBm,即4W时,读写器的工作距离可以达到7m。

2.2射频接收机

接收机电路主要包括相干解调器、运算放大器、比较器等,其主体结构如图3所示。相干解凋器采用I、Q正交解调。接收机的设计难点主要为同频接收。因为对于无源标签,在循环发送询问信号期间,读写器需要始终发送载波信号来给标签提供能量。

然而,从发射机到接收机的隔离一般在20dB以下,因此在接收机接收标签应答信号的同时也会接收到这个比较强的载波信号,这就要求接收机必须具有很高的线性度。对于这个问题,既不能像手机系统中那样采用双频收发,也不能像有些射频收发机那样采用分时收发,而只能通过提高接收机的线性度和增大发射机与接收机之间的隔离来解决。

本接收机中采用了一个高线性度低噪声的直接转换正交解调器LT5516,它的ldB压缩点可达6.6dBm,而噪声系数只有11.4dB。由于一般的低噪声放大器(LNA)的线性度不能满足要求,故在前端没有采用低噪声放大器。LT5516的RF输入端口与LO输入端口均采用差分输入,故在它的两个输入端口处各接了一个平衡,不平衡变换器Balun(图中未示出)。由于L1’5516的两个输入端口的输入阻抗为2001l,而外部的RF与Lo输入信号均是匹配在50Ω,故本设计中的Balun采用的是1:4的变压器,实现从单端信号到差分信号转换的同时也实现了从50Ω到200Ω的阻抗变换。

LT5516的输出是正交的I,Q两路信号,并且分别以差分形式输出。它的输出阻抗为60Ω,在输出端接了270pF的对地电容:从而获得截止频率位于10MHz的RC低通滤波器,以此滤出高频分量。

运算放大器和比较器采用了噪声较低的LT6207,它含有4个运算放大器,将其中两个作为第一级,另两个作为第二级。LT5516的输出差分信号经过低通滤波,采用交流耦合到第一级运算放大器的输入端,经放大后输出单端信号,然后再经直流耦合到第二级运算放大器的反相输入端。第二级运算放大器采用开环结构,实现电压比较器的功能,其同相输入端接比较电平。这样在第二级的输出端便可以得到数字信号,这就是射频接收机处理之后的信号。该信号将被送至数字基带处理模块进行进一步处理。

2.3数字基带处理模块

数字基带处理模块主要包括一个单片机、两个转换芯片、外部接口以及蜂鸣器等,其主体结构如图4所示。单片机采用了Philips的P89LPC932A1单片机,外部时钟频率为12MHz。整个系统的控制信号,如射频收发机中频率综合器的初始化信号、使能信号、跳频指令信号、相干解调器的使能信号以及ASK调制器的数字输入信号等均由这个单片机提供。另外,标签的应答信号经射频接收机接收处理后也需送至单片机进行解码、校验,然后由单片机作出判断,给出相应的卡号等信息。数字基带处理模块与读写器外部的接口包括RS232串口和USB端口,这里采用了两个转换芯片MAX3232和PL2303.分别实现从单片机到相应接口的信号转换,以此完成读写器与外部主机的通信。这样既可以由外部主机对读写器进行控制,也可以由读写器将读取的标签信息返回给外部主机。

功分器相关文章:功分器原理

评论