短波软件无线电通信系统中的DSP技术

随着无线通信频段的升高,由于受硬件器件的制约,在实现理想软件无线电过程中,有两种演进结构即中频数字化软件无线电结构和基带数字化软件无线电结构。本文详细讨论一种采用中频数字化软件无线电结构的实用短波软件无线电接收机中的数字信号处理技术。

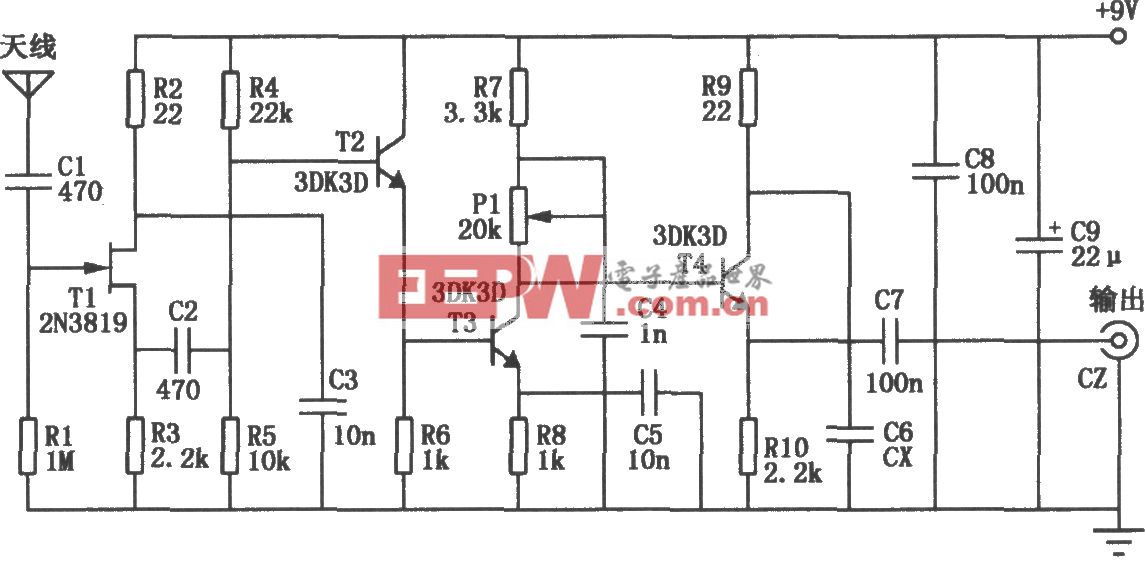

1 短波软件无线电接收机的硬件组成

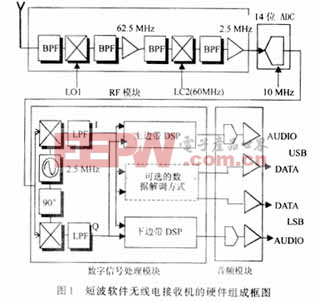

短波软件无线电接收机的硬件组成如图1所示。

图中射频转换模块(RF)包括2个混频器和相应的模拟滤波器,以产生合适的中频宽带信号;模/数转换部分,采用了二中频并行A/D转换方案,所选芯片为AD9240;数字信号处理模块中的数字下变频部分,其完成的功能主要有:下变频、滤除带外噪声、降低采样率等。主要指标有动态范围、抽取滤波器的性能、频率分辨率和输出信号的精度等。所选芯片为Harris公司生产的HSP50016; 数字信号处理模块中的数字信号处理部分,主要完成信息解调、控制射频前端和接收面板CPU的控制信号等任务。我们要求该部分的微处理器芯片速度快、精度高及具有较多便捷的信息传输通路和通信端口。所选芯片为TI公司生产的TMS320C31。信号接收过程为:天线接收到的高频信号(15 kHz~30 MHz)以后,与可调本地振荡器(LO1频率为:62.5~92.5 MHz)相混频,得到期望的第一中频信号(62.5 MHz),再与本地固定振荡器(LO2频率为:62.5 MHz) 混频产生第二中频信号(2.5 MHz)。然后对此中频信号用10 MHz的采样率进行A/D并行采样,采样后的数字信号处理采用专门数字处理器件HSP50016和通用DSP芯片(TMS320C31)联合处理方式,在数字信号处理模块,先采用数字下变频器HSP50016对该数字信号进行下变频、抽取,得到正交的2路I,Q号,然后再根据面板发出的解调方式来对信号进行解调及信号分析等。解调后把信号送往D/A口,对FSK调制方式来说,解调后信号直接送出数据(DATA)。

2 短波软件无线电接收机中的数字信号处理

2.1 数据流的输入

参见图1,在中频2.5 MHz上以10 MHz的采样率fs完成量化后,其14位的并行数据进入数字下变频器HSP50016,HSP50016把fs=10 MHz的14位并行数据变为24位的fs=39062.5 Hz的行数据送到DSP的串行口。在DSP里,通过串口中断接收这些数据。数据输出时,DSP将处理后的上、下边带信号以fs=39062.5 Hz采样率分别送往各自的D/A。

HSP50016输出数据的格式为先I后Q,循环如此,每对数据的发送率是39.0625 kHz(T=25.6 s)。UDSP是通过串口中断取得这些数据的。这就产生一个问题:UDSP怎么知道当前取到的数据是I还是Q呢?

通过对HSP50016的分析,我们知道,I,Q信号并非各占T/2。HSP50016发送I或Q所需时间是由串口时钟及数据长度决定的。我们定义HSP50016的串口时钟为5 MHz(不能定义为2.5MHz,因为信号的中心频率为2.5 MHz ,而串口时钟的幅度较大,这样会有一部分时钟信号渗漏到信号中,从而使解调的质量大大下降。),数据长度为24位,加上起始及停止位,共26位。

这样发送I所需时间为:![]()

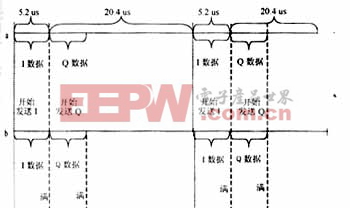

HSP50016发送I,Q数据与C31中断及定时器计数值之间的时序关系如图2所示。

图2(a)是HSP50016发送I,Q数据的顺序及时宽。

图2(b)是HSP50016发送I,Q数据的具体过程。

图2(c)是DSP串口的接收过程及串口中断的发出时机。

图2(d)表示DSP响应串口中断的过程及在I,Q中断期间定时器的记数情况。

根据式(1)及图2所表示的逻辑关系,我们只要在程序中设置一个定时器即可区分出I或Q信号。设定时器采用C31内部时钟(C31的工作频率为60 MHz),即计数频率为15 MHz,则发送I时可计数:

5.2×15=78个 (2)

而发送Q可计数:

20.4×15=306个 (3)

由式(2)、式(3)可得,当计数值>200时,此时发送的数据为I(实际值应该在306左右);反之则为Q。

评论