利用串行RapidIO实现FPGA协处理

同时,开发人员不但要跟上日益提高的性能需求,还得注意保持成本低廉 有效利用基于串行RapidIO的FPGA作为DSP协处理器就能达到这些目的

有效利用基于串行RapidIO的FPGA作为DSP协处理器就能达到这些目的

由于三重播放应用集合了话音、视频和数据应用,因此必须采用新算法来设定其开发和系统优化策略的参数 其间,开发人员要解决以下问题:构造可调整可扩展的架构、支持分布式处理、采用基于标准的设计,以及针对性能和成本进行优化

其间,开发人员要解决以下问题:构造可调整可扩展的架构、支持分布式处理、采用基于标准的设计,以及针对性能和成本进行优化

仔细研究一下就会发现,为满足应用需求而要、面对的这些挑战主要涉及两个主题:一是连接性,从本质上说就是实现不同设备、板卡和系统之间的“快速”数据转移;二是计算能力,指设备、板卡和系统中分别可用的处理资源

运算平台之间的连接

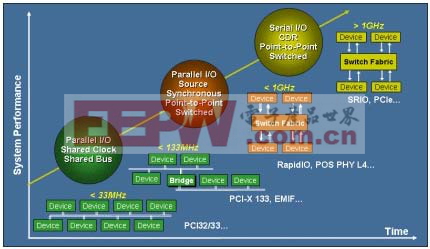

基于标准的设计通常比“自由发挥”的设计简单得多,也是今天的典型设计模式 并行连接标准(PCI、PCI-X、EMIF等)虽能满足当前需求,但若考虑到可调整性和可扩展性就有所不足了

并行连接标准(PCI、PCI-X、EMIF等)虽能满足当前需求,但若考虑到可调整性和可扩展性就有所不足了 随着分组处理技术的不断进步,连接标准的发展趋势显然倾向于高速串行连接

随着分组处理技术的不断进步,连接标准的发展趋势显然倾向于高速串行连接 从图1中就能看出这一趋势

从图1中就能看出这一趋势

诸如PCIe和GbE/XAUI之类的高速串行标准在台式机和网络行业已有应用 但无线通信设施中的数据处理系统对互连方面的要求又稍有不同,它要求:

但无线通信设施中的数据处理系统对互连方面的要求又稍有不同,它要求:

1. 管脚数少;

2. 需进行底板以及芯片到芯片的连接;

3. 带宽和速度可调;

4. 具备DMA和消息传递功能;

5. 支持复杂可调整的拓扑;

6. 支持多点传送;

7. 高度可靠;

8. 支持当日时间(time of day)同步;

9. 可提供服务质量(QoS)

图1:向串行连接的发展趋势

串行RapidIO (SRIO)协议标准可轻松满足以上大部分要求,甚至超出这些要求的标准 因此,串行RapidIO已成为无线通信基础设备中用于数据层(data plane)互连的主流连接技术

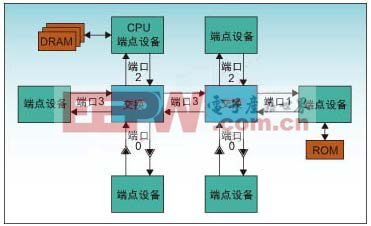

因此,串行RapidIO已成为无线通信基础设备中用于数据层(data plane)互连的主流连接技术 SRIO网络建立在两个“基本模块”基础之上:端点设备(Endpoint)和交换设备(Switch)

SRIO网络建立在两个“基本模块”基础之上:端点设备(Endpoint)和交换设备(Switch) 端点设备负责收发数据包,交换设备负责在端口之间传递数据包,但不负责数据包的解释

端点设备负责收发数据包,交换设备负责在端口之间传递数据包,但不负责数据包的解释 图2给出了SRIO网络的构建模块

图2给出了SRIO网络的构建模块

图2:SRIO网络的构建模块

按规范定义,串行RapidIO有用3层架构,如图3所示

图3:SRIO架构

其中包含:

物理层――负责描述器件级接口规范,例如分组传输机制、流量控制、电特性以及低级错误管理

评论