嵌入式编程需注意的Cache机制及其原理

1 Cache的原理

Cache即高速缓存,它的出现基于两种因素:一、CPU的速度和性能提高很快,而主存速度较低且价格高;二、程序执行的局部性特点。将速度较快而容量有限的SRAM构成Cache,可以尽可能发挥CPU的高速度。CPU与外设交换数据时经常用到buffer(缓冲),这与缓存极其相似,只不过Cache是为了提高CPU和内存之间的数据交换速度而设计,而buffer是为了提高内存和硬盘(或其他I/O设备)之间的数据交换速度而设计的。

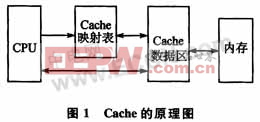

Baidu快照(cache.baidu.com)就是一个缓存的例子,其作用与计算机CPU缓存有类似之处。 Cache的原理如图1所示。

在读取内存数据的同时CPU将数据保存到Cache数据区,同时更新Cache映射表(保存地址信息,表示该地址的数据是否已在Cache数据区,即是否命中)。这样,CPU再次读取该地址数据时,就可以直接从Cache提取。读Cache的时间远小于直接读内存,可提高CPU读取数据的效率。

Cache数据区有成块读取的特性(Cache映射表保存的地址是块地址,节省空间,也符合程序执行的局部性特点)。Cache数据区远远小于内存空间,就需要相应的替代算法。比如最近最少使用算法,可将新数据替代使用频率低的数据,同时更新映射表信息。可以推想,Cache空间越大,命中率越高。

写内存需要直接更新内存。如果映射表存在该地址信息,还需要同时更新Cache数据区。这种Cache访问方式就称作“直写”,Samsung公司的ARM7微处理器S3CA510B就是这种方式。以下所讨论的Cache问题除非特殊说明,否则都是“直写”方式。

2 嵌入式编程时需注意的问题

2.1访问外设使用Cache的问题

在访问内存时使用Cache是不会出现问题的,但如果访问数据易变外设(数据不依赖于CPU写操作而改变)时使用Cache就可能出现问题。问题在于外设数据的改变不仅仅依靠CPU写操作,CPU第一次读取外设数据时将外设的数据和地址信息保存到Cache,第二次读取外设数据时就可能有问题出现。这是因为数据直接从Cache提取,而外设的数据可能有改变。

因此,在访问易变外设时要禁止使能Cache,直接读取外设数据到CPU,而不经过Cache的任何环节,即保证不改变Cache映射表和Cache数据区内容。

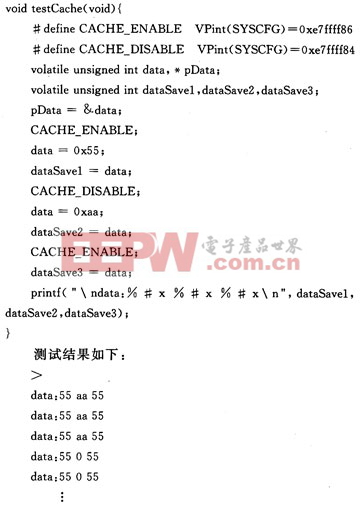

S3C4510B的SYSCFG SFR(特殊功能寄存器)有用来控制Cache使能或不使能的,通过对该SFR的设置可暂时禁止Cache或重新恢复Cache功能。这样就可以在读取外设前禁止Cache,读取结束后重新使能Cache,保证了外设数据读取的正确性。写数据到外设时采用“直写”方式,更没有问题。

2.2开关Cache引发的新问题

在Cache开关期间,如果有另一个进程/任务访问内存,在此期间写内存并且该内存在Cache中已有映射(注意,它也是被禁止Cache的,所以它不会同时更新Cache数据区的内容),那么在Cache重新使能之后Cache数据区的信息已经过时了,而Cache映射表还是Cache禁止之前的状态,如果CPU此时读数据就会得到过时的数据。这样看来,引发的问题范围更广了,连内存的数据读写正确性都无法保证。与内存泄漏的影响来比较,内存泄漏如果是一颗定时炸弹,那么Cache问题就可以说是随时随地都可能踩上的雷区,因为程序一旦开始就可能引发爆炸。

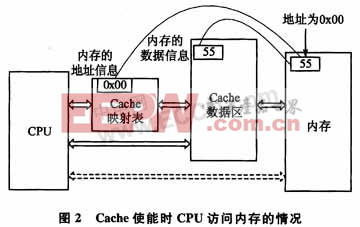

如图2所示,Cache使能时Cache映射表和Cache数据区保存了内存的数据信息,这是CPU访问内存时通过图中实线箭头通路实现的。内存的信息可以与Cache的信息保持一致。

Cache禁止时的情况有所变化。由图2中虚线箭头通路直接进行内存访问,且地址0x00处的数据由55变为AA,但Cache区的信息仍为之前的状态。很明显,Cache的数据是应该废弃的,但是Cache映射表仍保存0x00的地址信息。Cache重新使能后,CPU再次读取0x00地址的数据,由于Cache仍是命中,直接从Cache数据区中提取数据,这样读出来的数据就是0x55了。

由S3C4510B数据手册第4节的第21页可知:通过对SYSCFG寄存器的CE位置1或清0可使能/关闭Cache,但是Cache没有内容自动刷新功能,在重新使能Cache时需考虑Cache数据的正确性。

为了证实以上说法,循环执行如下测试程序:

评论