千兆位设备PCB的信号完整性设计

本文主要讨论在千兆位数据传输中需考虑的信号完整性设计问题,同时介绍应用PCB设计工具解决这些问题的方法,如趋肤效应和介质损耗、过孔和连接器的影响、差分信号及布线考虑、电源分配及EMI控制等。

本文引用地址:http://www.amcfsurvey.com/article/156237.htm通讯与计算机技术的高速发展使得高速PCB设计进入了千兆位领域,新的高速器件应用使得如此高的速率在背板和单板上的长距离传输成为可能,但与此同时,PCB设计中的信号完整性问题(SI)、电源完整性以及电磁兼容方面的问题也更加突出。

信号完整性是指信号在信号线上传输的质量,主要问题包括反射、振荡、时序、地弹和串扰等。信号完整性差不是由某个单一因素导致,而是板级设计中多种因素共同引起。在千兆位设备的PCB板设计中,一个好的信号完整性设计要求工程师全面考虑器件、传输线互联方案、电源分配以及EMC方面的问题。

高速PCB设计EDA工具已经从单纯的仿真验证发展到设计和验证相结合,帮助设计者在设计早期设定规则以避免错误而不是在设计后期发现问题。随着数据速率越来越高设计越来越复杂,高速PCB系统分析工具变得更加必要,这些工具包括时序分析、信号完整性分析、设计空间参数扫描分析、EMC设计、电源系统稳定性分析等。这里我们将着重讨论在千兆位设备PCB设计中信号完整性分析应考虑的一些问题。

高速器件与器件模型

尽管千兆位发送与接收元器件供应商会提供有关芯片的设计资料,但是器件供应商对于新器件信号完整性的了解也存在一个过程,这样器件供应商给出的设计指南可能并不成熟,还有就是器件供应商给出的设计约束条件通常都是非常苛刻的,对设计工程师来说要满足所有的设计规则会非常困难。所以就需要信号完整性工程师运用仿真分析工具对供应商的约束规则和实际设计进行分析,考察和优化元器件选择、拓扑结构、匹配方案、匹配元器件的值,并最终开发出确保信号完整性的PCB布局布线规则。因此,千兆位信号的精确仿真分析变得十分重要,而器件模型在信号完整性分析工作中的作用也越来越得到重视。

元器件模型通常包括IBIS模型和Spice模型。由于板级仿真只关心输出管脚经过互联系统到输入管脚的信号响应,同时IC厂家不希望泄漏器件内部详细的电路信息,且晶体管级Spice模型仿真时间通常难以忍受,所以IBIS模型在高速PCB设计领域逐渐被越来越多的器件厂家和信号完整性工程师所接受。

对于千兆位设备PCB系统的仿真,工程师经常会对IBIS模型的精确性提出质疑。当器件工作在晶体管的饱和与截止区时,IBIS模型缺乏足够详细的信息来描述,在瞬态响应的非线性区域,用IBIS模型仿真的结果不能像晶体管级模型那样产生精确的响应信息。然而,对于ECL类型器件,可以得到和晶体管级模型仿真结果很吻合的IBIS模型,原因很简单,ECL驱动器工作在晶体管的线性区域,输出波形更接近于理想的波形,按IBIS标准可以得到较为精确的IBIS模型。

随着数据传输速率提高,在ECL技术基础上发展起来的差分器件得到很大发展。LVDS标准和CML等使得千兆位信号传输成为可能。从上面的讨论可知,由于电路结构和相应的差分技术应用,IBIS标准仍然适用于千兆位系统的设计。已发表的一些IBIS模型在2.5Gbps LVDS和CML设计中的应用文章也证明了这一点。

由于IBIS模型不适用于描述有源电路,对于许多有预加重电路进行损耗补偿的Gbps器件,IBIS模型并不合适。因此,在千兆位系统设计中,IBIS模型只有在下列情况下才可以有效工作:

1.差分器件工作在放大区(线性V-I曲线)

2.器件没有有源预加重电路

3.器件有预加重电路但是没有启动(短的互联系统下启动预加重功能可能导致更差的结果)

4.器件有无源预加重电路,但是电路可以从器件的裸片上分离。

数据速率在10Gbps或以上时,输出的波形更像正弦波,这时Spice模型就更适用。

损耗影响

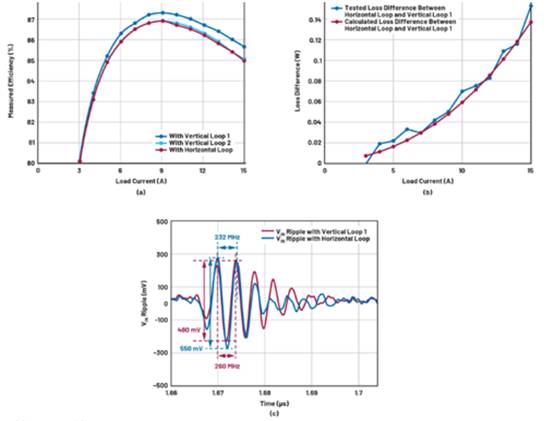

当信号频率升高,传输线上的衰减就不可忽略。此时需要考虑由导体串连等效电阻和介质并联等效电导引起的损耗,需使用有损传输线模型进行分析。

评论