波特率连续可调的串口通信技术

摘要 在基于PCI接口波特率连续可调的串口通信技术中,串口通信模块作为整个PCI接口功能的本地模块,是实现PCI接口模块与外部串口信息的沟通。文中介绍了波特率连续可调技术的实现原理和方法,并基于PCI接口和FPGA技术完成通信模块的实现与测试验证。其具有设计的灵活性和应用的广泛性。

关键词 PCI接口;串口通信;波特率连续可调;DDS;FPGA

基于PCI总线的串口通信技术,在工业领域中有着重要的应用。而目前市场上基于PCI总线的串口通信卡,虽然可以实现多串口收发且波特率可调,但可调的波特率只是几个点,不能实现连续可调。但在一些军事通信中,经常会需要波特率连续可调,以满足军事通信中对波特率的特殊要求。文中基于这个要求,采用硬件描述语言,实现这一功能要求在FPGA上的研究、开发、测试与验证。

1 波特率连续可调的串口通信

1.1 串口通信中的波特率技术

在数据通信中,波特率等于每秒钟传输的数据位数。在串行通讯中,收发双方基于同一波特率实现数据的发送与接收。波特率即为发送或接收信号的频率。

1.2 波特率连续可调的DDS方法

1.2.1 设计要求

例如RS232标准中串行通信波特率的一般要求范围是300~115 200 bit·s-1。而传统的串行通信卡支持波特率可调只是在某几点可调。文中研究的目标是波特率连续可调,例如要求波特率在300~115 200 bit·s-1之间可以实现步进为1 bit·s-1甚至0.1 bit·s-1的调节。

改变波特率即改变信号发送或信号接收时钟的频率,可以采用对基准时钟进行数据分频的方法,但达不到调节的连续性。文中采用改进的DDS方法,实现对发送时钟fclk步进为1 bit·s-1的调节。

1.2.2 DDS原理介绍

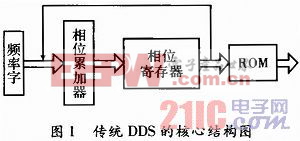

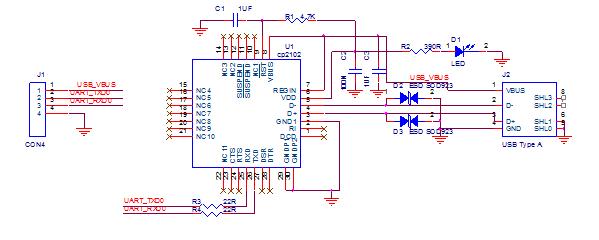

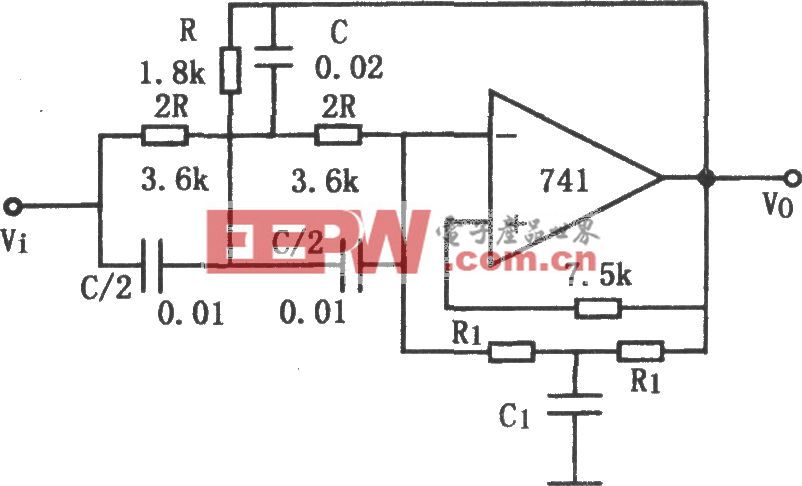

直接数字频率合成DDS(Direct Digital Synthesis)是种把一系列数字信号通过D/A转换器转换为模拟信号的合成技术。传统DDS的核心结构如图1所示。

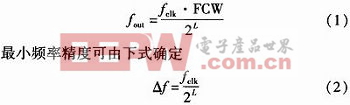

输出频率可由式(1)确定。

其中,fclk是时钟频率;FCW是频率控制字;L为相位累加字的字长。

1.2.3 产生频率连续可调的时钟信号

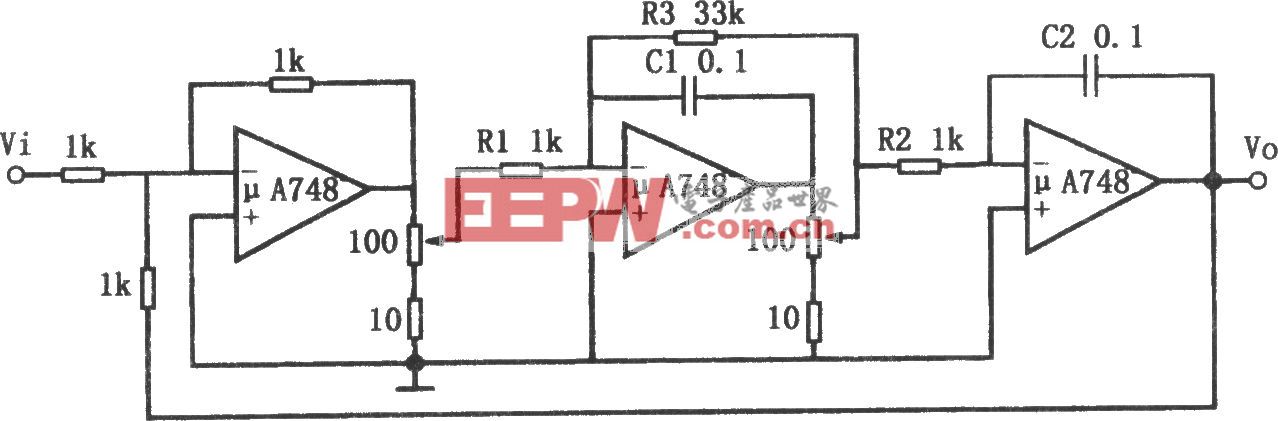

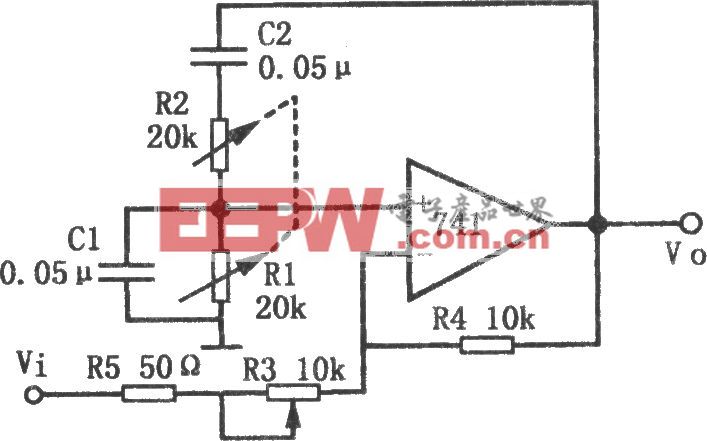

在传统的DDS技术中,频率最小步进值的尾数不是零,给后续的频率合成造成不便,所以采用改进的DDS技术,循环相位累加器设定一个可调的最大值作为溢出值,最大值溢出后,以余值而不是以零作为下一次累加的起始值。结构框图如图2所示。

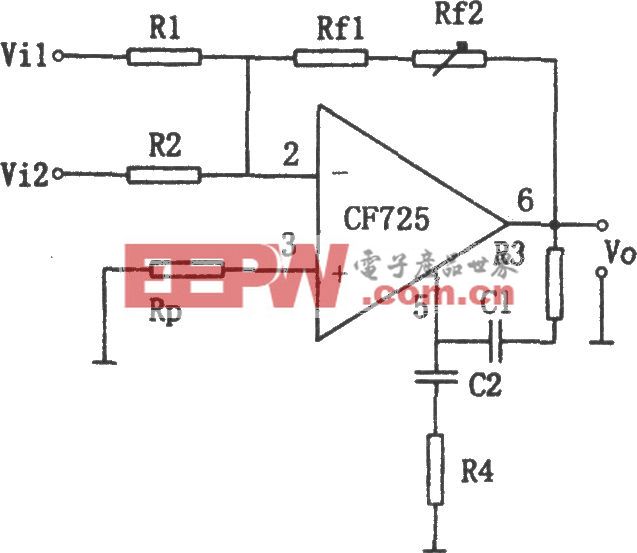

改进后的DDS输出频率可由式(3)确定

![]()

最小频率精度可由式(4)确定

![]()

评论