基于TMS320C6713的USB数据传输系统设计

摘要:介绍了基于TMS320C6713的USB数据传输系统。该系统以TMS320C6713作为主控制器,通过CY7C68001USB控制器连接TMS320C6713与PC主机,克服了传统的数据传输量小,传输速度慢的缺点,能更好地满足大容量数据的传输要求。在此详细阐明了系统的硬件设计方案和软件设计思想,并进行实现。结果证明,研制的系统具有传输速率高,可靠性好的优点。

关键词:高速数据传输;USB 2.0;DSP;VC++

0 引言

近年来,随着DSP技术的不断发展,数据采集和处理技术已经广泛应用于通信、雷达、遥测遥感等各个领域。声信号数据采集具有采集量大,速度快的特点,因此,在DSP与主机进行数据传输时,需要采用高速通信接口。传统的接口一般采用PCI总线或RS 232串行总线。PCI总线传输速率可达132 Mb/s,但其扩充槽有限且插拔不方便;RS 232串行总线连接比较方便,但是传输速率太慢,不易用于高速传送数据和传送大量数据。随着计算机技术的不断发展,越来越多的计算机不再为用户提供PCI和RS 232外部接口,USB逐渐成为统一的标准外设接口。通用串行总线(USB)集中了PCI和RS 232串行总线的优点,具有方便的即插即用和热插拔特性以及较高的传输速率。其中,USB 2.0的速率最高可达480 Mb/s,满足高速数据传输的要求。

该系统采用TMS320C6713,配合嵌入USB 2.0协议的芯片CY7C68001,实现了PC主机与DSP间的高速数据传输。

1 芯片介绍

TMS320C6713为高性能32位浮点DSP,适用于专业音频信号处理,其主频可达300 MHz,处理速度高达2 400 MIPS/1 800MFLOPS。其内部采用改进的哈佛结构;具有256 KB的片上存储空间;丰富的外设包括2个多通道缓冲串口(McBSP)、2个多通道音频串口(McASP)、SPI和I2C等;增强的直接存储器访问(EDMA)控制器,可控制16个独立通道完成不受CPU干预的数据传输;32 b的外部存储器接口(EMIF),能与SRAM,ERPOM,FLASH,SBSRAM和SDRAM无缝连接。

Cypress公司的CY7C68001集成了USB 2.0收发器(物理层)以及USB 2.0串行接口引擎SIE(链路层,实现底层通信协议),可工作在USB 2.0高速和全速状态。它的最高速度可达480 Mb/s,具有2个外部接口,均可通过同步或异步方式进行访问。其命令接口用来访问CY7C68001寄存器、Endpoint0寄存器以及描述表,FIFO数据接口用来访问4个1 KB的FIFO。

2 硬件设计

TMS320C6713通过EMIF的CE3存储空间可以外扩USB 2.0接口,因此在对外扩USB进行读/写访问前,需要通过EMIF的CE3控制寄存器CE3CTL来配置CE3空间的存储器接口的类型、存储器宽度及读写时序(建立时间、系统时间、保持时间等),具体配置在USB程序配置中详细给出。

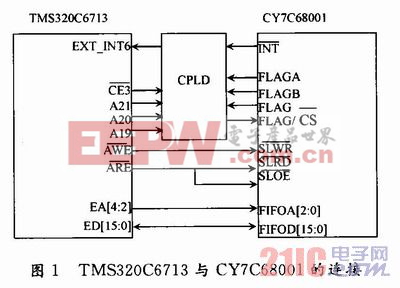

CY7C68001采用并行异步存储器接口通过可编程逻辑芯片CPLD与TMS320C6713相连接。其原理框图如图1所示。

由于在USB数据传输过程中,EMIF接口的片选信号会长时间片选CE3空间,因此,需要避免TMS320C6713在USB数据传输过程中使用通过EMIF接口通过其他CEX空间外扩的SDRAM、SBSRAM等存储器,否则会造成USB数据的错误传输。

CY7C68001除了存储器接口外,还有1个中断信号![]() 和4个状态信号(READY,FLAGA,FLAGB和FLAGC)。中断信号

和4个状态信号(READY,FLAGA,FLAGB和FLAGC)。中断信号![]() 采用TMS320C67 13的外部中断EXT_INT6。

采用TMS320C67 13的外部中断EXT_INT6。

评论