小型化低功耗数字信号处理器设计

摘要:随着电子技术的不断进步,一些原本只能安装在较大平台的通信设备通过小型化、低功耗设计已经能够加装在较小的平台上,而通信设备的加装会使这些平台的信息化程度大幅提升,从而适应更多的应用场合。为了实现通信设备的小型化和低功耗,文章给出了通信信号处理器的小型化和低功耗设计方法。

本文引用地址:http://www.amcfsurvey.com/article/154901.htm关键词:NCO;FPGA;DSP;数字上变频器

0 引言

随着各类武器平台向信息化、网络化的方向发展,各类小型、超小型平台,如空空导弹、小型无人机等,对通信设备的需求日趋迫切。此类平台由十体积小、载荷低,采用电池供电,无法承载主要由模拟部件或半数字化部件组成的结构尺寸、重最、功耗都较大的通信设备。尤其是通信信号处理器,由于受到关键元件技术水平的限制,其结构尺寸、功耗等往往无法实现小型化,因而严重制约了通信设备适装超小型平台的技术可行性。

数字电路技术的突飞猛进使得通信信号处理器的小型化成为可能。以大容量、高速FPGA以及低功耗、大位数、高采样速率A/D转换器为核心的新一代数字处理器技术,使原先需要大量数字元件实现的功能都被集成到了几个可编程的元件中,故可使得电路的面积缩小到原先的十分之一到几十分之一,同时整体功耗却降低了一半以上。如扩频通信中的核心处理部件(相关器)用模拟器件实现时,其体积将很大,且信号处理能力较低,无法满足码速率超过5 Mbps的信号速率。而以大容量FPGA为电路基础构件的数字处理系统,则彻底剔出了模拟信号处理系统的种种缺陷。因此,只要选取合适硬件资源的FPGA,就可以将若干个数字相关器集嵌入到单一的一片FPGA中,而不改变任何电路面积。

高速A/D技术的进步,已经使通信信号处理器由模拟电路发展为数字中频处理器系统,其中频信号可通过A/D采样转换成单纯的采样数字流,从而真正实现信号处理算法的全数字化。

1 设计架构和部件选择

1.1 通信信号处理器的电路构架

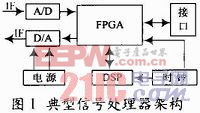

最小化通信处理器架构可由FPGA+DSP构建,图1所示就是一种典型的信号处理器架构图。其中,FPGA用于完成上下变频、编译码、调制解调、同步捕获等信号处理算法;DSP则用于完成信息的打包、拆包以及一些复杂协议的处理。

1.2 高集成度低功耗数字处理部件的选型

设计低功耗、小型化信号处理系统的关键是在保证系统性能的前提下,精简不必要的功能,同时选择功耗最优的芯片来构建最优电路配置。

(1)A/D采样器的选择

A/D采样器的选择既要考虑A/D采样器的性能,又要满足系统所要求的动态范围和性能指标。评估A/D采样器的性能指标主要有采样位宽、无杂散动态范围(SFDR)、信噪比(SNR)、转换速率、量化灵敏度等。一般采样宽度越宽,动态范围越大。

凌特公司推出的14位125Msps双通道高速模数转换器LTC2285,其单通道功耗仅395 mW,采用9 mm×9 mm的QFN封装,可以为高速小型化低功耗设计提供有力帮助。LTC2285与典型的14位采样器AD6645相比,具有不可比拟的优点。表1所列是这两种器件的主要参数比较。

(2)数字上变频器的选择

AD9957内部集成有大最的硬件资源,包括正交数字上变频器、滤波器、时钟倍频器、D/A转换器、增益控制器、参数寄存器、波形存储RAM、SPI接口控制器等。通过对AD9957内部信号参数寄存器的配置,可产生多种复杂波形。其正文输入信号速率达250 MHz,模拟输出信号频率最高可达400 MHz,且相位噪声小于125 dBc/Hz。

通过内置的8个键控波形存储寄存器,可以通过控制信号对所存储波形进行切换,以实现MSK、BPSK QPSK、8PSK、MFSK等多种高速率的调频、调相信号。14 bit的D/A可实现84 dB输出信号动态范围。

(3)FPGA的选择

FPGA是数字信号处理器的核心器件,主要负责完成编码、调制、滤波、同步、解调、解码等处理过程。FPGA的选型首先要满足信号处理器的需求,同时要兼顾系统功耗。

ARRIA II GX系列是ALTERA公司的中档级FPGA,具有快速收发器、LVDS和存储器,能以低成本和低功耗实现丰富的功能。EP2AGX125具有124100个LE、18×18乘法器576个、高速收发器12个,而且性能适中,适合处理码速率在20 Mbps以下、中频载频低于200 MHz的中频采样系统;而STRATIX系列FPGA性能比较高,它含有更多的硬件资源,但功耗过大;功耗最低的CYCLONE系列FPGA的处理能力较弱,适合于码速率5 Mbps以下、中频载频70 MHz以下的中频采样系统。

(4)DSP的选择

DSP也是通信信号处理系统不可缺少的硬件资源,例如数据的打包/解包、统计、调度、信道参数的下发、低实现性的信号处理算法通过DSP编程实现起来比较容易。同样的处理功能,若采用FPGA逻辑电路实现难度极大,同时消耗的硬件资源巨大,虽然可以通过并行运算大幅提高算法速度,但由于电路复杂度过高,因而会带来不必要的设计障碍和调试困难。尤其是对于大量浮点数据的处理,DSP相对FPGA具有较大的优势。

通常,DSP的选型关键是内核处理能力和总线吞吐能力两个技术指标。如果需要系统进行浮点数据处理,还应考虑其浮点数据的处理能力。根据工程经验,对于低功耗通信信号处理的应用场合,DSP内核应选取低于300 MHz的定点或浮点处理器,外总线位宽在32 bit以下,外总线吞吐能力高于通信码速率5~10倍以上即可,这样可以在每个时隙的末尾快速读取或下发收/发数据。一般DSP内核的速率不必太高,因为大量的实时信号处理已经通过FPGA完成,DSP仅作为后端数据处理部件,因此,过高的内核时钟会带来不必要的功耗开销。

综上所述,ADI公司的ADSP 21369是较为符合以上技术特点的低功耗、高性能浮点DSP,该器件的内核时钟最高可达333 MHz,32 bit外总线可工作在10 MHz以上速率,对于20 Mbps信道码速率通信系统具有16倍的数据吞吐能力,而该芯片全速工作的功耗也不会超过1 W,是较为理想的通信信号处理器数据处理部件。

2 小型化低功耗设计

根据现有技术水平和信号处理器小型化、低功耗设计的技术要求,结合应用场合的实际要求,并以处理基带码速率为20 Mbps,以BPSK信号为调制方式的通信系统为例,给出以最优数字电路配置来构建小型化、低功耗信号处理器设计方法。

本系统的A/D采样器采用LTC2285。若以双通道14 bit位宽、80 Mbps采样速率来对输入载波频率为100 MHz、码速率20 Mbps的BPSK信号进行带通采样,可满足20 dB以上动态范围的设计需要。此外,该芯片的休眠功能特别适合时分多址体制下的低功耗需求。当系统处于发射时隙或休止时隙时,可以关闭A/D采样器内核,使其处于最小工作状态,从而进一步降低功耗。另外,LTC2285采用单电源供电,外围电路设计简单,也对降低电路复杂度和规模帮助较大。

该数字中频处理系统中的核心处理器件采用ALTERA公司的EP2AGX12515,其内部资源可满足对两路A/D采样器输入的80 MHz数据流进行相关信号处理,包括正交基带下变频、数字低通滤波、数字相关,正交相关峰合成、载波相位跟踪、同步捕获、定时点提取等数字信号处理。该FPGA内部的大量乘加器资源还可实现高速率、高阶数的FIR滤波器。

评论