基于LXI总线的1553B通讯模块设计与开发

2.3 宏功能模块RAM生成

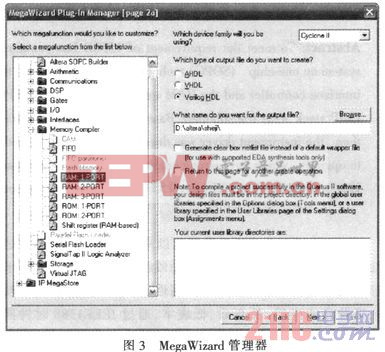

CycloneII器件内部的RAM块只有M4K一种,可用来实现真正的双端口、简单双端口和单端口的RAM,可以支持移位寄存器和ROM方式。用QuartusII内所带的MegaWizard管理器来生成RAM,首先运行MegaWizard管理器选择“创建一个新的宏功能”,在出现的对话框内选择Insta lled Plug-Ins下的memory compiler下的RAM:1-PORT,如图3所示。本文引用地址:http://www.amcfsurvey.com/article/154578.htm

在接下来的各页中选择如下参数:数据线宽度16位;存储64个字;自动单时钟驱动;选择生成*.v,*.bsf,*_inst.v,*_bb.v,*_waveforms.html 5个文件。其他参数默认即可。

2.4 以太网接口设计

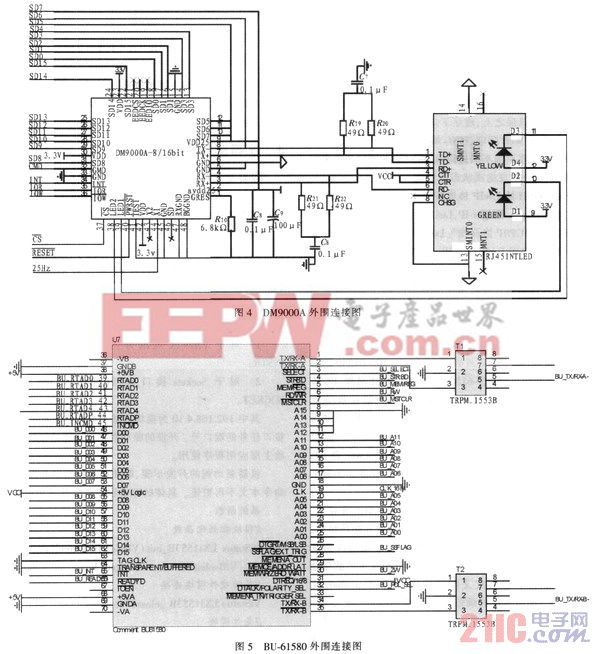

以太网控制器选用DM9000A,芯片为48管脚的LQFP封装,支持处理器接口以字节/字模式的I/O命令操作内部存储器数据,集成10/100M带有AUTO-MDIX的接收器,支持用于全双工流控制的IEEE802.3x标准,提供IP/TCP/UDP校验和生成以及校验过程,可选的EEPROM配置。

DM9000A与控制器和RJ45连接器的连接如图4所示。DM9000A与控制器有两种数据总线宽度的连接方式,即8位/16位模式,论文选用16位操作模式。DM9000A通过TX+、TX-、RX+和RX- 4条线与自带隔离变压器的RJ45转换器相连。RESET引脚为DM9000A的复位引脚,低电平有效;X1外接25 Hz时钟频率。

tcp/ip相关文章:tcp/ip是什么

评论