RapidIO技术测试思路分析

RapidIO总线的出现及其体系结构和应用

本文引用地址:http://www.amcfsurvey.com/article/154028.htm传统总线多采用并线总线的工作方式,这类总线一般分为三组:数据线,地址线和控制线。实现此类总线互连的器件所需引脚数较多,例如对于64位数据宽的总线,一般由64根数据线,32-40根地址线以及30根左右的控制线,另外由于半导体制造工艺的限制还要加上一定数量的电源引线和地线,总共会有约200根左右的引线,这给器件封装、测试、焊接都带来了一些问题,如果要将这种总线用于系统之间的通过背板的互连,由此带来的困难就可想而知。并线总线的另一个问题是时钟与信号的偏移容限的问题,对于这样一组并行信号线的集合,信号的采样是取决于时钟信号的上升沿或是下降沿,这样对于信号的跳变和时钟的跳变时刻的时间差就有一个上限值,随着速率的升高,布线长度、器件门电路自身的翻转时间都会影响总线的速率。

用于处理器之间互连以及背板互连的另一个主要技术是以太网,近些年来,以太网在存储、电信、通讯、无线、工业应用以及嵌入式应用中得到大量的应用,现有的成熟的硬件和协议栈降低了开发的复杂性和产品的开发成本。但是在局域网和广域网中得到很好应用的以太网用于这种芯片级或是板极的系统互连显示出了低效率、高延时的特性,QOS需要高层软件的参与,造成软件模块化结构不清晰。尤其是当背板的传输速率从1Gbps增加到10Gbps时,增加的处理要求已经超出了以太网的能力。

RapidIO技术最初是由Freescale和Mercury共同研发的一项互连技术,其研发初衷是作为处理器的前端总线,用于处理器之间的互连,但在标准制定之初,其创建者就意识到了RapidIO还可以做为系统级互连的高效前端总线而使用。1999年完成第一个标准的制定,2003年5月,Mercury Computer Systems公司首次推出使用Rapid IO技术的多处理器系统ImpactRT 3100, 表明RapidIO已由一个标准制定阶段进展到产品阶段,到目前为止,RapidIO已经成为电信,通迅以及嵌入式系统内的芯片与芯片之间,板与板之间的背板互连技术的生力军。

RapidIO是针对嵌入式系统的独特互连需求而提出的,那么我们首先来说明嵌入式系统互连的一些基本需求:嵌入式系统需要的是一种标准化的互连设计,要满足以下几个基本的特点:高效率、低系统成本,点对点或是点对多点的通信,支持DMA操作,支持消息传递模式交换数据,支持分散处理和多主控系统,支持多种拓朴结构;另外,高稳定性和QOS也是选择嵌入式系统总线的基本原则。而这些恰是RapidIO期望满足的方向。所以RapidIO在制定之初即确定了以下几个基本原则:一是轻量型的传输协议,使协议尽量简单;二是对软件的制约要少,层次结构清晰;三是专注于机箱内部芯片与芯片之间,板与板之间的互连。

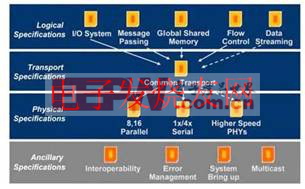

RapidIO采用三层分级的体系结构,分级结构图如下图所示:

图1:RapidIO三层分级体系结构图

由此图可见,RapidIO协议由逻辑层、传输层和物理层构成。最明显的一个特点就是RapidIO采用了单一的公用传输层规范来相容、会聚不同的逻辑层和物理层,单一的逻辑层实体增强了RapidIO的适应性。物理层定义了串行和并行两个实体,得到广泛应用的只有串行方式,尤其是用在背板互连的场合,串行方式可以在两个连接器之间允许80-100cm的连线,单链路传输带宽可达10Gbps。目前RapidIO的标准是Version1.3,在未来的Version2.0规范中定义了更高的传输速率,可以得到更高的传输带宽。

目前,RapidIO在无线基站系统中已经得到了广泛的应用,同样在视频处理,语音处理,高性能计算机及存储领域也会得到越来越多的应用。在实现芯片到芯片之间、板与板之间的高速互连上,RapidIO所能带来的好处也越来越直观,对于简化系统设计、高带宽、低延时等特点也被开发人员广泛接受。下一代的RapidIO在应用上也要向机箱与机箱间的高速互连方向上发展,同时也会提供更高的传输速率,2.0规范中已经可以实现40Gbps的带宽。我们相信,随着越来越多的处理器支持RapidIO接口,RapidIO的应用前景会越来越光明

众所周知,当今世界数字技术飞速发展,无论您是一位从事电信产品或是数据通信产品,PC,服务器及相关产品,高速半导体集成电路设计,或是高速光电收发模块,高速信号处理,高速互连器件(诸如高速接插件,高速数字传输电缆)等领域的研发及测试工程师都会面临着一个共同的挑战——Signal Integrity(SI)——信号完整性。

大概10年前我们所提到的数字产品,其时钟或数据频率大多在几十兆之内,信号的上升时间大多在几个纳秒,甚至几十纳秒以上。那时的数字化产品设计工程师进行的就是“数字设计”DD只要掌握布尔代数等数字方面的诸多知识,保证逻辑正确,就能设计出其所期望的性能的产品。而现在的数字技术已经发展到几千兆,甚至几十千兆的传输速率,信号的上升时间大多在一纳秒以内,诸如串扰,阻抗匹配,EMI(电磁兼容),抖动等射频微波领域才会遇到的问题,如今变成了高速数字设计必须解决的关键性问题。这就要求我们的工程师不但要具备数字方面的设计知识,同时也要具备射频微波方面的设计知识;不但要掌握时域及逻辑域的测量技术,还要掌握频域的测量技术。

高速数字设计与测试在欧美,日本等技术先进国家近些年来已成为一个非常热门的行业,它是实现高性能数字化产品的基础,就如同一个城市的道路建设,只有路修得好,车才能跑得既稳又快。因此,国内外很多大公司都相继成立了高速数字设计与测试(信号完整性分析)的研发力量。

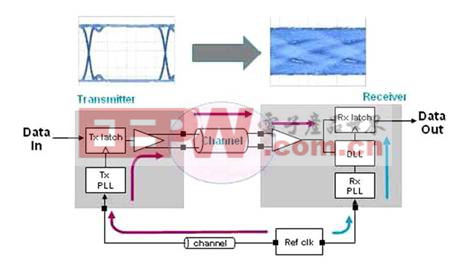

图2:典型的高速互连系统

图2是一个典型的高速互连系统,包括:发送器,传输通道和接收器。针对这种高速互

连系统(如RapidIO互连系统)的信号完整性测试分析,我们需要考虑三个方面:

1、 信号波形参数测试分析:一般用示波器测试分析发送端的信号或接收端的信号,通

过眼图/模板、抖动等参数的测试分析决定是否满足规范或设计要求。

2、 互连测试分析:这是从引发波形失真的源头去测试,测试通道的差分阻抗,衰减等

参数,分析是否会引发信号完整性问题。

3、 接收性能测试:只是信号波形好不能保证整个系统误码率一定很低,系统一定稳定

和可靠,因为接收性能的好坏也是决定系统性能和稳定性的一个关键方面。

首先我们需要考虑的是信号波形参数测试分析部分。信号波形参数测试分析一方面检测被测系统是否满足规范或设计的要求,另一方面是帮助我们找到问题的根源。图3是安捷伦信号波形参数分析解决方案。DSA90000A数字信号分析仪带宽从2.5GHz到13GHz可选和带宽可升级,采样速率每通道高达40GSa/s,存储深度最深每通道达1GB。DSO9000A带宽从1GHz到4GHz可选和带宽可升级,采用速率最高达20GSa/s,存储深度最深达1GB(两通道使用下每通道指标),卓越的性能满足RapidIO测试的要求。

注:测试3.125Gbps的RapidIO需要8GHz带宽,测试2.5Gbps的RapidIO需要6GHz

带宽,测试1.25GHz的RapidIO需要4GHz的带宽。

图3:安捷伦信号波形参数分析解决方案DSA90000A和DSO9000A

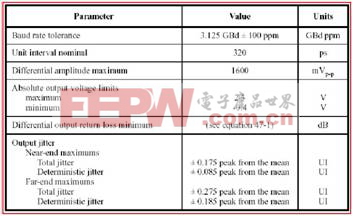

针对串行RapidIO,信号波形参数测试内容如下(以3.125G为例):

表1:串行RapidIO信号品质测试规范(以3.125Gbps为例)

评论