充分发挥多核优势

在当今日益复杂的互连世界里,现有应用、不断发展的应用以及新兴应用都将为片上系统 (SoC) 的性能要求造成影响。为满足性能与成本目标要求,功能不断演进,这为设计人员深入探索他们正在思索的多核解决方案架构基础创造了契机。在理想条件下,多核 SoC 架构包含以下特性:

本文引用地址:http://www.amcfsurvey.com/article/153976.htm· 支持多种类型的执行引擎(内核),包括数字信号处理器 (DSP)、矢量信号处理(VSP) 以及精简的指令集计算 (RISC);

· 提供全面的多核优势,将器件全部功能用于预期应用实现业界领先的性能;

· 使各种器件实现重复使用;

· 引入软件产业生态系统以减轻编程工作量,缩短开发时间。

本文将介绍 SoC 所需的各种架构元素,帮助用户获得理想的器件特性,实现媒体服务器与无线基带基础设施等高级通信基础设施应用。

多核、多层 SoC 架构

SoC 的概念是指将越来越多的功能集成到给定器件中,使该器件能够执行目标应用所需的近乎全部或全部功能的一种基本方法。SoC 体现在硅芯片器件中,而整体解决方案则往往整合了大量的软件。许多 SoC 设计将 DSP 内核与 RISC 内核配对来满足特定应用处理需求,比如媒体网关中的语音处理及转码,或者无线基础设施中的无线电通道及传输网络处理等。

过去,性能改善是通过工艺节点升级和提高时钟频率实现的。在当前的小型几何构造工艺节点中,提高时钟频率和升级工艺节点在提高性能的同时也会导致成本上升,因而权衡分析更加复杂。

作为替代方法,可实施多重处理内核,在较低时钟频率及较低功耗下,满足所有系统参数要求的同时提供所需的高性能。这种方法已作为多核 SoC 嵌入式应用的优先选择出现。此外,还可整合专用加速技术与协处理器进一步提升性能,降低系统功率。在这种情况下,支持处理资源的并行访问非常重要,这样可全面发挥器件优势。在芯片基础设施中提供相关功能对 SoC 架构而言至关重要,这样互连功能可全面发挥多核优势。对此最直接的方法是大型交叉点矩阵,但这种方法在功耗与成本上不占优势,因为在任何时间点上都有一大部分矩阵,即使在没有使用的情况下都需要供电。更高级的片上网络方法,可为密切相关的处理元素提供本地功能,以及供这些本地化功能互连的共用主干网。

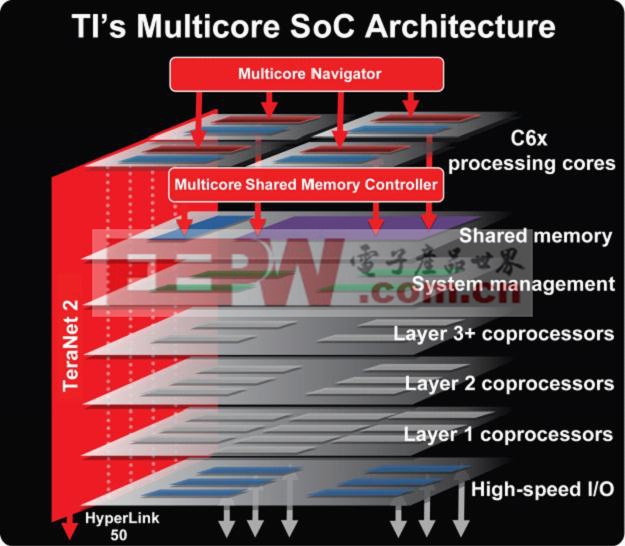

推动摩尔定律发展

采用更高级工艺节点,一直是跟上摩尔定律发展的重要推动力。升级到 40 纳米 (nm) 工艺带来了显著的性能提升,升级到 28 nm 也是如此,但当今应用需求更高。今天,新工艺节点带来的最大优势是,有可能将更多的应用功能集成到单个器件中。因此,它是一项实现 SoC 的关键使能器。利用这种集成潜力提高性能的最明显也是最早的方法是,添加可编程内核。多核器件可分为同质与异质两类。同质指所有处理内核均相同,而异质则指混有各种类型的内核。实际上,几乎所有的应用都要求包括信号处理与控制代码在内的混合处理功能。DSP 内核与 ARM® RISC 内核是这种混合处理的理想选择。德州仪器 (TI) 提供的最新 DSP 内核不但可同时支持定浮点运算,而且还可在高时钟速率下执行 VSP,从而可简化算法的开发与部署。所提供的各种 ARM 内核可帮助 SoC 提供商根据处理要求、功耗以及工艺节点优化 RISC 内核选择。从架构角度上讲,支持同质内核实施很重要。同质器件(所有的 ARM 或所有的 DSP)可通过异质架构创建,但反之如果不严重影响性能,则很难实现。图 1 是 TI 最新 KeyStone 多核架构的示意图,这是异构多核架构的实例。

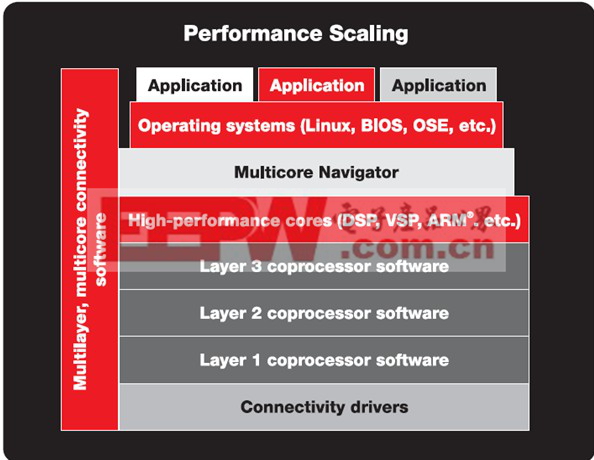

图1:TIKeyStone多核架构

该架构由采用同一方式封装的多个功能元素构成,可提高应用灵活性与可扩展性。 高度灵活的架构经过精心设计,可便捷地根据应用要求添加或移除元素。无线基站与雷达阵列处理等应用具有极其相似的处理与 I/O 需求,但具有极为不同的加速与协同处理需求。1 层 PHY 加速器对无线基站而言是必不可少的,但雷达阵列处理却并不需要。虽然同一机构既开发雷达产品又开发基站产品的可能性不大,不过他们仍可从 SoC 开发商提供的低成本与大容量优势中获益。 在提供各种产品时,SoC 架构的可扩展性对添加或移除处理元素,满足不断变化的需求非常重要。今天,无线基站从小型蜂窝毫微微产品,到大型多蜂窝宏基站应有尽有。同样雷达制造商也需要既有小型产品,也有大型设备。 简化软件产业环境生态系统 多核 SoC 开发商通常提供和预集成大量非差异化软件,即与任何终端设备制造商提供的功能相同的基本软件,包括设备驱动器、实时操作系统 (RTOS) 端口以及针对目标应用的主要标准化算法等。正确实施后,这种软件不但可为应用开发人员充分发挥硅芯片优势,而且还可随时投入生产。除这种多核 SoC 之外,厂商还创建了开发产业环境生态系统,可为应用开发、测试以及电路板设计提供帮助。 图 2:综合多核工具套件示例 对开发人员来说,在为多核环境编写代码,特别是当应用代码需要从小型器件缩放至大型器件时,多核开发会变得具有挑战性。在出现这种情况时,软硬件都要在各种器件中缩放。此时系列间的器件内核数量及硬件加速器,可能存在巨大的差异。 幸运的是,由于软件的复杂性以及多核 SoC 中处理元素的变化,硬件辅助软件已经实现。用于简化多核软件开发的创新新硬件现已嵌入在最新一代多核器件中。该硬件可自动辅助软件缩放,以在源自通用架构的各种器件间使用。

评论