RS-485 数据速率独立型半双工中继器设计

21ic讯工程师们经常面临的一个问题是,如何为 RS-485 应用设计一款非数据速率依赖型半双工中继器。例如,通过给现有网络添加分接头,设计一款超出建议最大线缆长度 (1200m) 的远距离网络,或者设计一款星型拓扑网络。各种系统所使用的数据速率并不相同,从 10 kbps 到 200 kbps,不一而足。

本文引用地址:http://www.amcfsurvey.com/article/153846.htm远程节点之间的接地电位差 (GPD) 所产生的电压,超出了大多数总线收发器的最大共模电压范围,因此必须在网络节点电子组件和总线之间实施电隔离。

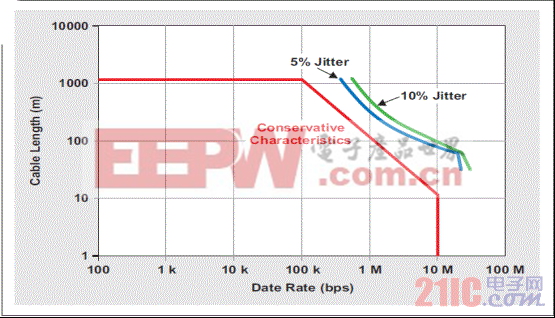

线缆长度与数据速率的对比特性表明,应使用 1200m(4000英尺)的最大线缆长度(图 1)。使用该长度时,常用 120-Ω、AWG24 无屏蔽双绞线 (UTP) 的电阻接近端电阻器值,并使总线信号摆幅减小一半(6 dB)。

图 1 线缆长度与数据速率的关系

在 RS-485 技术文献中,为了简便起见,收发器产品说明书通常会介绍一种全双工中继器设计。但是,在远距离传输网络中,数千个仪表都使用全双工线缆并不可取,因为线缆和配线都非常的昂贵。

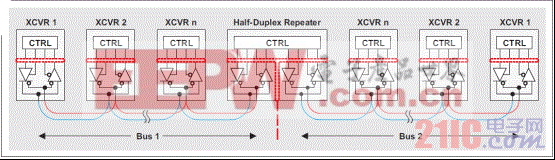

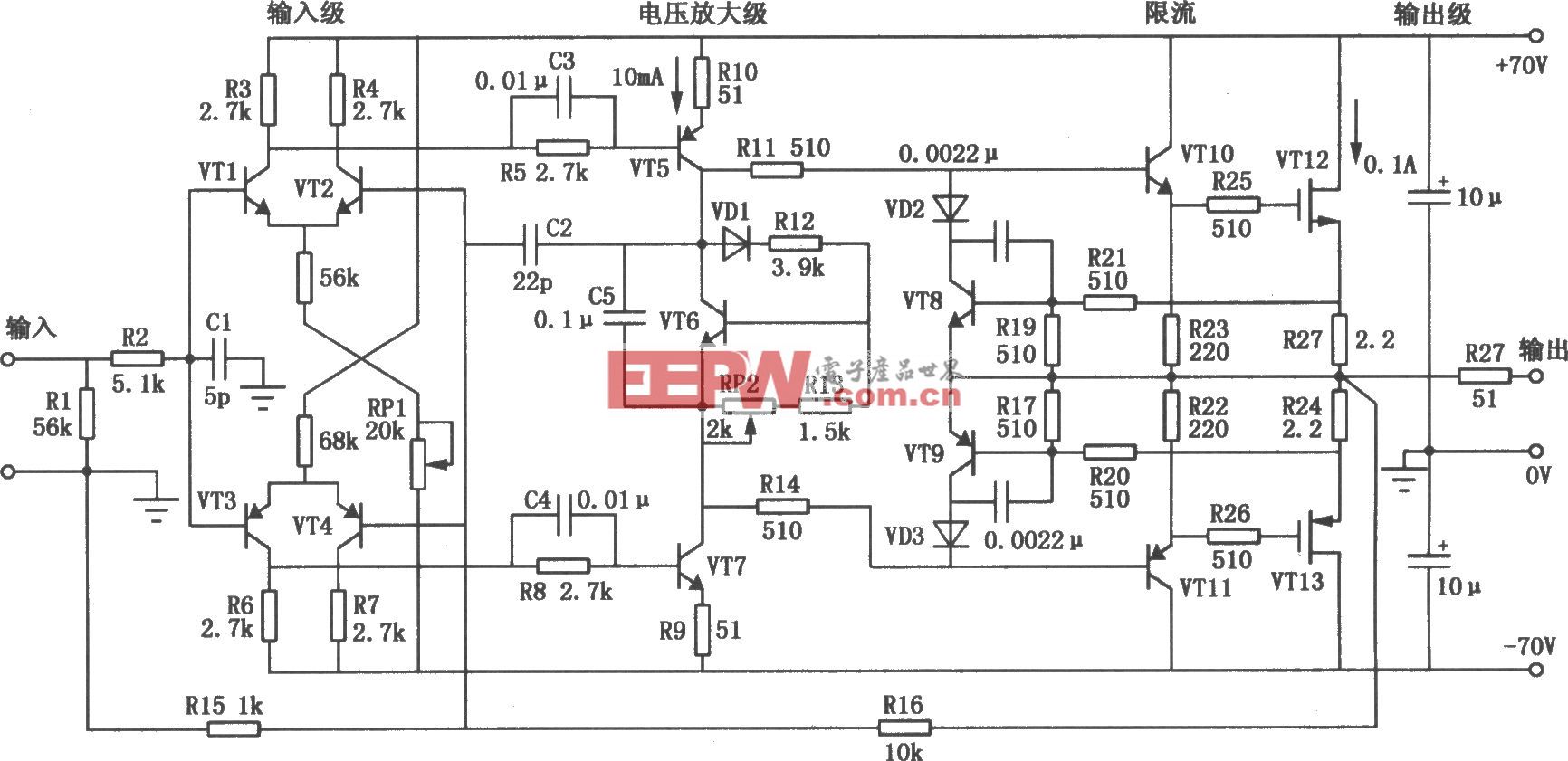

为了实施一款更远距离的半双工模式远距传输网络,我们必须安装一个半双工中继器。图 2 显示了一个系统结构图。由于半双工中继器连接至两个总线段,该中继器必须包含两个独立的收发器,每个收发器都经由信号隔离器连接至其各自总线,并连接至一个隔离于两个收发器部分的控制逻辑。该控制逻辑及时关闭和开启中继器的驱动器和接收机部分。任意方向的发来数据信号都可对其初始化。

图 2 双隔离半双工中继器总线扩展

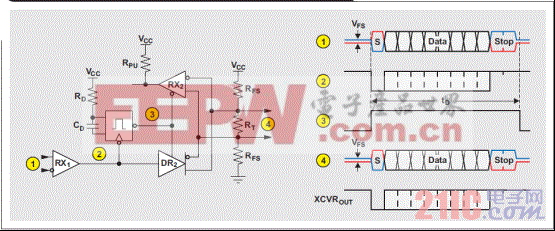

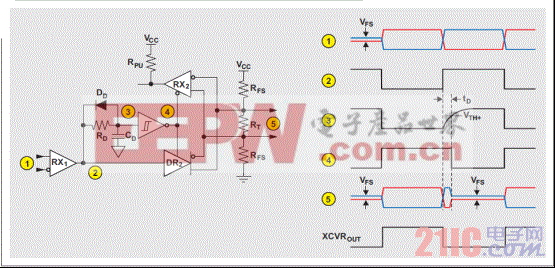

两种最为常用的时序控制方法是图 3 所示单触发电路和图 4 所示时延反相缓冲器电路。为了确保正确的开关行为,两种方法都要求对上电和总线闲置以后的启动条件进行定义。通过故障保护偏压电阻器 RFS 可以完成这项工作,其在没有收发器有效驱动总线时,产生一个大于接收机输入敏感度 VFS > +200 mV 的故障保护电压 VFS。

图 3 利用一个单触发电路实施的收发器时序控制

图 4 利用一个反相缓冲器电路实施的收发器时序控制

完整执行一遍单触发电路的功能运行顺序(此处以数字编号,请参见图 3),清楚地说明了该中继器的工作过程:

1、 在总线闲置期间,由于VFS,两个中继器端口的接收机输出均为高电平。因此,两个收发器在接收模式下相互牵制。

2、 接下来,端口 1 上发来数据包起始位的到达,驱动 RX1 输出为低。这种转变触发单触发电路,从而驱动其输出为高,并激活驱动器 DR2。

3、 正确计算时间常量 RD × CD,以使该单触发电路输出在整个数据包时间期间都保持高态。

4、 在单触发时间常量期间,DR2 始终驱动总线 2。XCVROUT 代表总线 2 上远程收发器的接收机输出状态。请注意,DR2 被激活时,上拉电阻器 RPU 拉高未激活接收机 (RX2) 的输出,以使 RX1 保持激活状态。

这种解决方案的缺点是,R-C 时间常量取决于数据包长度和发送信号的数据速率。另外,单触发电路易受噪声瞬态的影响,容易引起伪触发和中继器故障。

不过,单触发电路常用于接口桥接,例如:RS-232 到 RS-485 转换器等。这些转换器直接把 RS-485 网络连接至老式 PC 或者 RS-232 控制机器的 RS-232 端口。

有一种更加稳健和不依赖于数据速率的方法可以替代单触发电路,即通过一种具有不同充电和放电时间的反相施米特 (Schmitt) 触发缓冲器,实现时序控制。优先原则是在逻辑低状态期间主动驱动总线,并在逻辑高状态期间关闭驱动器。然后,根据逐位原则开启和关闭序列,从而使中继器功能独立于数据速率和数据包长度。

完整执行一遍反相器控制中继器的功能运行顺序(此处以数字编号,请参见图4),可以清楚地说明其运行过程:

1、 在总线闲置期间,由于 VFS,两个中继器端口的接收机输出均为高。延迟电容 CD 获得完全充电,驱动反相器输出为低态,以使收发器维持在接收模式下。

2、 之后,总线 1 出现一个低位,驱动RX1输出为低电平,快速对 CD 放电,并激活驱动器 DR2。

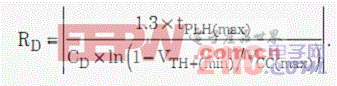

3、 当总线电压变为正(VBus > 200 mV)时,RX1 输出变为高,其驱动 DR2 输出为高,并通过 RD 对 CD 缓慢充电。必须正确计算最小时间常量(RD × CD),以使最大电源电压 VCC(max) 和最小正反相器输入阈值VTH+(min) 时,延迟时间tD 超过驱动器最大低到高传播延迟 tPLH(max),即超出 30%。例如,电容为 CD = 100 Pf 时,RD 的要求电阻值为:

4、 根据延迟时间 (tD) 与实际数据位间隔时间的对比情况,延长驱动器激活时间,以在总线建立有效的高态信号。需在从发射模式切换至接收模式以前完成这项工作,目的是让接收机输出始终保持高态。由于接收机传播延迟短于驱动器,因此接收机不可能变为低态,即使是一瞬间的低态都不可能。驱动器一旦关闭,外部故障保护电阻器便将总线 2 偏压至 200 mV 以上,其被活跃接收机看作是一个定义高电平。

评论