隔离式LVDS接口电路

评估和设计支持

本文引用地址:http://www.amcfsurvey.com/article/153734.htm电路评估板

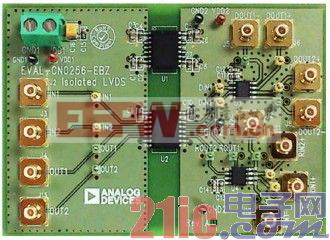

CN-0256 电路评估板(EVAL-CN0256-EBZ)

设计和集成文件

原理图、布局文件、物料清单

电路功能与优势

低压差分信号(LVDS)是低功耗、高速、点对点通信的既定标准(TIA/EIA-644)。它用于在仪器仪表和控制应用中通过背板或短电缆链路传输大量数据,或分配高速时钟至应用电路的不同部分。

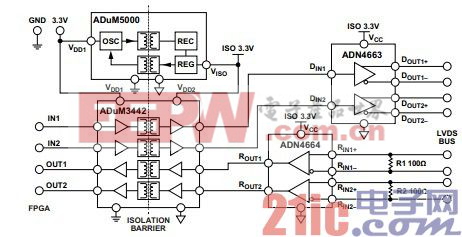

图1所示电路表示LVDS接口的隔离。隔离LVDS接口的好处有:保护器件免受故障影响(安全隔离) ,以及增加鲁棒性(功能隔离)。

ADuM3442为ADN4663 LVDS驱动器的逻辑输入以及ADN4664LVDS 驱动器的逻辑输出提供数字隔离。除了使用ADuM5000提供隔离式电源,在工业和仪器仪表应用中隔离LVDS链路还面临着许多挑战,包括:

• 逻辑信号与LVDS驱动器/接收器隔离、确保电路总线端的标准LVDS通信。

• 高度集成的隔离仅使用两个额外的宽体SOIC器件(ADuM3442 和ADuM5000 ) 来隔离标准LVDS 器件(ADN4663和ADN4664)。

• 与传统隔离(光耦合器)相比功耗更低。LVDS应用的特性之一是低功耗工作。

• 多通道隔离。LVDS应用中,使用并行通道以尽量增大数据吞吐量。本电路演示4通道隔离(本实例中采用两条发射通道和两条接收通道)。

• 工作速度高;最高工作速度达150 Mbps,轻松满足基本LVDS的速度要求。

图1所示电路隔离了一个双通道LVDS线路驱动器和一个双通道LVDS接收器。它可在单电路板上实现两条完整的发射和接收路径。

图1. 隔离式LVDS接口电路(原理示意图,未显示所有连接)

CN-0256

电路描述

隔离式LVDS 的应用包括安全隔离和/或电路板间、背板和印刷电路板(PCB)通信链路的功能隔离。例如当LVDS背板系统的一个或多个插卡有遭受高电压瞬变的风险时,便可使用安全隔离。隔离LVDS接口可确保这类故障条件不影响系统中的其他电路。某些情况下使用功能隔离很有效,例如测量设备。若在ADC和FPGA之间隔离LVDS链路,则可提供浮动的接地层,提升测量数据的完整性,并降低来自应用的其他部分的干扰。

图2表示隔离式LVDS接口电路,它隔离两个发射通信通道( C M O S / T T L 至LV D S ) 和两个接收通道 ( LV D S 至CMOS/TTL) 。隔离信号的数据速率最高可达150 Mbps,此速率下还可保持ADuM3442 的最大脉冲宽度失真规范。

图2. 隔离式LVDS接口电路

逻辑电平可施加于IN1和IN2 ,并且被ADuM3442 隔离。ADuM3442 对应的输出(DIN1和DIN2 测试引脚)连接至ADN4663 LVDS 驱动器,以便在DOUT1+ 、DOUT1− 和DOUT2+ 、DOUT2−上建立LVDS信号。

ADN4664 LVDS接收器可在RIN1+ 、RIN1−和RIN2+ 、RIN2−上接收LVDS信号。接收器输出(ROUT1 、ROUT2测试引脚)连接至ADuM3442 ,以便隔离信号。ADuM3442对应的逻辑输出为OUT1和OUT2。

电路通过连接VDD1从逻辑端供电。电源可以是3.3 V或5 V ,为ADuM3442(电路信号隔离)的逻辑端供电或为ADuM5000供电,ADuM5000则为电路总线端提供隔离式电源。

ADuM5000 的输出VISO可为LVDS驱动器(ADN4663)和LVDS接收器(ADN4664)以及ADuM3442的总线端提供3.3 V电源。

采用了AN-0971应用笔记“isoPower器件的辐射控制建议”指南中的描述进行电路布局。此外,该布局针对高速差分信号优化。LVDS输入/输出走线长度匹配,并具有50 Ω的对地阻抗(差分对之间的阻抗为100 Ω)。每对测试点与驱动器/接收器同样距离匹配。多个接地过孔排列在走线旁边以增加高速工作时的信号完整性。LVDS 的输入RIN1+ 、RIN1−和RIN2+ 、RIN2−连接100 Ω的端电阻(R1 、R2) 。将任意连接到DOUT1+ 、DOUT1−和DOUT2+ 、DOUT1−的总线接收端进行端接。电源和接地通过螺旋电缆连接器互相连接(VDD1和GND1) 。逻辑输入(IN1 、IN2)/输出(OUT1 、OUT2)通过4个SMB连接器互相连接。总线信号通过8个SMB连接器以相似的方式连接。它们通过走线以对地50 Ω的阻抗连接LVDS驱动器(ADN4663)和接收器(ADN4664)。

电路评估与测试

若要对隔离式LVDS接口电路板供电,在VDD1上施加3.3 V或5 V 电源。检查VDD2测试点的电压水平以测试该电路是否正确供电。该测试点是ADuM5000提供的隔离式电源,额定值应为3.3 V或5 V。

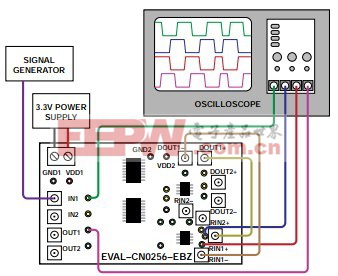

完整的发射和接收通道可通过将LVDS输出的一条通道连接至LVDS输入的一条通道进行测试。例如,要测试通道1 ,则:DOUT1+与RIN1+相连;DOUT1-与RIN1-相连;连接可使用SMB至SMB导联。

信号发生器或模式发生器可连接至IN1 ,并且OUT1测试点(或OUT1连接器)的输出必须匹配输入。测试设置如图3所示。

图3. 发射和接收通道1的测试设置

图4 中的示波器曲线图表示IN1 、RIN1+ 、RIN1−和OUT1的测试波形,测试时在IN1上采用50 Mbps时钟信号,DIN1+和RIN1+ 、DIN1−和RIN1−之间采用90 cm屏蔽导联。

DIY机械键盘相关社区:机械键盘DIY

评论