基于ARM926EJ-S的MPEG-4软解码器的优化与实现

1 引 言

本文引用地址:http://www.amcfsurvey.com/article/152648.htmMPEG-4视频压缩标准自问世以来受到人们的广泛关注。近几年,嵌入式应用中对MPEG-4播放器的实现已经成为众多厂家的研究热点。专用的MPEG-4播放芯片已经非常普遍,但是减少功耗和降低成本一直是商家追求的目标,因此,随着嵌入式的主流微处理器ARM的处理能力越来越强,用他来实现MPEG-4系统的软解码成为了众多嵌入式设计公司研究的重点内容。由于MPEG-4系统庞大且需要大量的数据处理,因此在ARM中实现MPEG-4软解码需要对其原算法进行充分的优化才能达到理想的性能。为此研究了一种基于ARM926EJ-S微处理器的MPEG-4解码算法的纯软件实现和优化的方法,通过对解码算法的软件优化,将QVGA格式MPEG-4码流在ARM9平台上的播放速度由原来的10 f/s提高到了37 f/s,完全达到了流畅播放的要求,具有很高的实用价值。

2开发平台及耗时分析

论文研究使用的是基于ARM926EJ-S微处理器的综合开发平台,采用Linux操作系统,外接320*240(QVGA格式)的LCD显示屏。ARM926EJ-S微处理器的时钟频率为190 MHz;采用5级整数流水线操作,支持32位ARM指令集和16位Thumb指令集以及扩充的DSP指令集;支持数据Cache和指令Cache,具有更高的指令和数据处理能力。软件编译环境为ADS1.2,使用Multi-ICE下载程序。

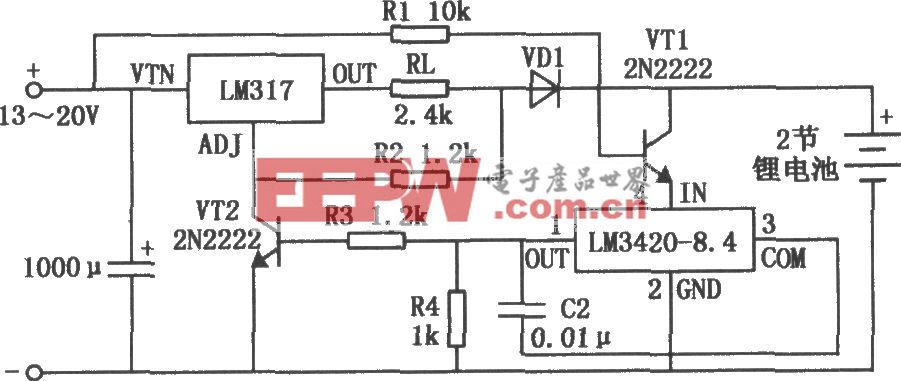

MPEG-4 SP级算法流程图如图1所示。优化的前期工作首先要将MPEG-4解码代码移植到开发平台上,然后对解码各个模块进行运算量和耗时分析,找出优化的重点内容。本文采用长度为376 934 B的AVI码流为测试序列,该码流共95帧,其中包括8个I帧,87个P帧。在未优化前测得的耗时分析结果如表1所示,整个测试序列解码播放完毕耗时10.05 s,解码播放速度只有9.5 f/s。

|

在ARM上用软件实现MPEG-4解码器的主要任务是提高解码速度,同时达到理想的画面播放效果。因此,怎样使耗时部分根据ARM处理器的特性提高程序执行效率是我们的主要工作,也是研究实现的重点。

3 MPEG-4解码算法在ARM926EJ-S上的优化

MPEG-4软解码以开源的XVID源代码做为参考,将XVID的C源代码移植到ARM平台上,在此基础上进行优化并测试优化后的解码播放性能。优化主要从3个方面进行:

(1)对XVID源代码的软件结构,程序流程进行适合ARM特点的调整。

(2)对运算量较大、耗时较多的模块编写汇编函数代替C程序模块,提高程序执行效率。

(3)寻找快速或并行算法。

3.1软件结构的优化

ARM的资源非常有限,在软件的结构安排上应尽量减少存储器访问,增加Cache的命中率,提高程序执行效率。

3.1.1 适当的模块合并处理以减少存储器的访问次数

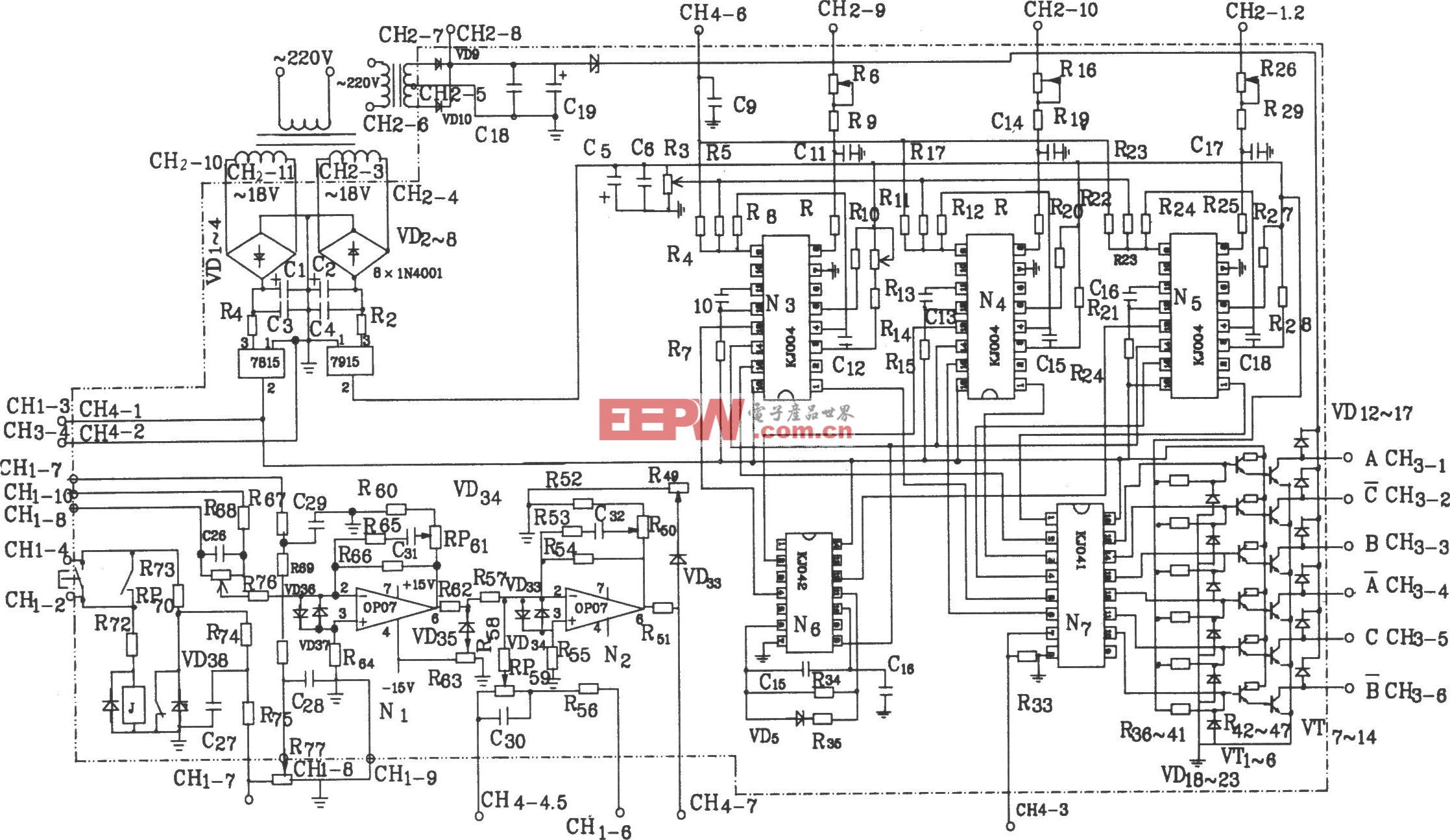

优化前的源代码中,I帧与P帧的宏块解码软件结构如图2所示。在这个流程中,对于inter宏块,可变长解码(VLD),反扫描(Iscan),反量化(Iquant)三个过程中有3次的Block存储区读,2次Block存储区写和1次Data存储区写。然而这些数据的处理并不存在关联性,为减少存储器访问带来的浪费,可以将在Block存储区读取的数据将这三个步骤全部进行完之后再放回存储区。因此可对这三个步骤进行合并处理。具体的做法是:将原来的两个函数:

合并后VLD从Block缓冲区读数据处理后马上进行反扫描和反量化,并将反量化后的数据存入Block中。整个过程只进行了一次Block缓冲区的读和写,不仅减少了两个读写操作,还减少了一个Data缓冲区的开辟。同时,对于P帧在VLD之后立即进行反量化还省去了大量零值的处理,这也是考虑合并的主要因素之一。

同样,I帧中的AC/DC预测和反量化也可以进行合并。做法是:将add_acdc(pMB,i,block[i*64],iDcScaler,predictors);dequant_intra(data[i*64],block[i*64],iQuant,iDcScaler)两个函数合并为:add_acde(pMB,i,block[i*64],iDcSealer,predictors,cbpcontrol,iQuant)。这个过程在减少存储器的读写操作的同时也减少了没有预测的AC值的反量化过程。

通过以上两个步骤的合并处理,由测试序列测试之后发现解码播放完毕耗时5.23 s,速度提高了将近9 f/s,效果非常明显。

|

相关推荐技术专区 |

评论