一种嵌入式视频记录系统的设计与实现

20世纪90年代以来数字多媒体技术取得了飞速的发展和广泛的应用,超大规模集成电路及专用视频压缩处理芯片随之迅速发展,同时随着半导体存储技术的发展,半导体存储器的容量也越来越大,这为研制数字化的音视频记录系统提供了有力的技术基础。同时数字化的记录方法将视频数据经过压缩记录在大容量的半导体存储器上,能有效消除噪声、加快拷贝和复制速度,快速回放和查找,同时还可以通过计算机网络进行传送,与传统的磁带式记录系统相比有着巨大的优势。基于此,作者设计实现了一种基于嵌入式控制模块DIMM-PC/520IU和专用视频处理芯片SZ1510硬件平台的MPEG-1编码标准的数字视频记录系统,该系统集成度高、功耗低、体积小、成本低,适合大量的各类视频监控和记录应用。

本文引用地址:http://www.amcfsurvey.com/article/152500.htm1 系统框架及原理说明

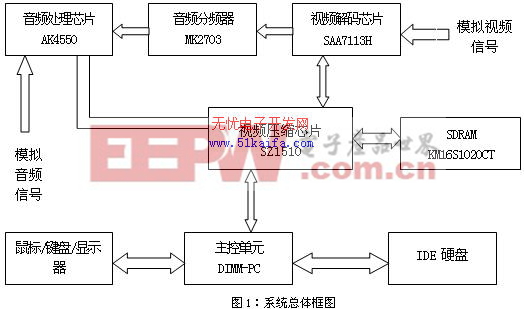

本系统选用的主要模块是主控单元DIMM-PC/520IU[1]和视频压缩芯片SZ1510,周围外部设备有视频解码芯片SAA7113H,音频分频器MK2703,音频解码芯片AK4550, RAM芯片,ROM芯片,IDE硬盘和电源模块。系统总体框图如图1所示。系统加电后[2],主控单元DIMM-PC调用程序,对视频压缩芯片SZ1510和视频解码芯片SAA7113H、音频解码芯片AK4550进行初始化配置;模拟视频信号传送给视频解码芯片SAA7113H进行解码,生成CCIR视频信号,AK4550采集输入的模拟音频信号,生成PCM数字音频流,分别送入压缩编码芯片SZ1510,压缩成MPEG-1格式的视频流,主控单元DINMM-PC将其以文件形式存储到IDE硬盘。为解决音视频同步问题,音视频同步采用视频源的同步信号锁定音频编码系统时钟的方式。芯片SAA7713的LLC管脚输出27MHz时钟,经分频器驱动,一路未分频信号校准SZ1510的系统时钟,另一路经过分频器MK2703作为音频编码输出系统时钟。该27MHz信号在SZ1510内部倍频至54MHz对输入的音视频数据进行同步。

2 MPEG-1压缩算法的基本原理

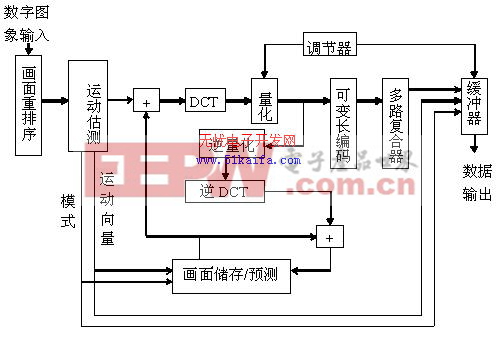

MPEG-1视频压缩技术是针对运动图像的数据压缩技术[3]。为了提高压缩比,帧内图像数据压缩和帧间数据压缩技术必须同时使用。帧内算法与JPEG压缩算法大致相同,采用基于DCT的变换编码技术,用于减少空域冗余信息。帧间压缩算法,采用预测法和插补法,预测法有因果预测器(纯的预测编码),和非因果预测即插补编码。预测误差可再通过DCT变换编码处理,进一步压缩。帧间编码技术可减少时间轴方向的冗余信息。从而在上述几个方面达到了对图像冗余信息的高效压缩。MPEG-1视频压缩的基本原理如图2所示。

图2 MPEG-1压缩的基本原理框图

3 硬件设计

3.1 控制模块设计

系统控制模块我们选择了Kontron公司DIMM-PC/520IU,采用AM5x86TM CPU,具有16KB 片内一级缓存,芯片组是ElanTM SC520集成,运行频率133MHz,工作电压为5V电压,支持DOS、Linux、WinCE、Vxworks等多种操作系统,存储温度为-40℃~80℃,工作温度0℃~60℃。DIMM-PC的所有模板使用了一种通用的DIMM-144内存插座作为连接件,采用144线的金手指连接方式,其CPU模板和扩展模板的插座略有区别,以防插错,几个扩展模板间没有区别,可以随便接插就象ISA插槽一样。CPU模板144接线分为几类ISA总线信号SD[0:15]、SA[0:19]数据地址信号;IOW、IOR、SMEMR等各种读写控制信号,OSC、SYSCLK、DRQ、DACK等特别功能信号,包含了标准ISA总线上的所有数据信号。

3.2 视频音频编解码模块设计

视频解码器采用Philips公司的SAA7113H,是一种从模拟到数字转换的9位视频输入处理器(VIP)[4],它是能与MPEG-1编码芯片SZ1510实现无缝接口的视频解码器之一。它由两通道的模拟预处理电路组成,包括源选择、自动钳位电路与ADC、自动增益控制、时钟产生电路、数字多标准解码器、亮度、对比度、饱和度控制电路和一个色度空间矩阵。解码器是基于行锁定时钟解码原理,能解码PAL和NTSC的色度信号为CCIR-601的颜色分量值。SAA7113H对输入的视频进行采样,解码后生成8 bit/像素的CCIR-601数字视频流,其电路由I2C总线控制[5]。音频解码器采用AK4550,它对模拟音频进行高信噪比16bit数字采样,生成PCM数字音频流。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论