基于AT91RM9200的嵌入式网络摄像机的设计与实现

本文引用地址:http://www.amcfsurvey.com/article/152449.htm

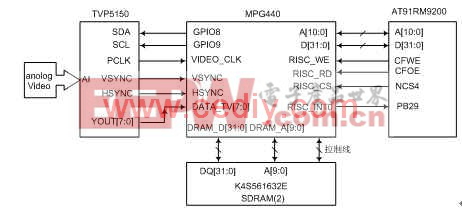

本文引用地址:http://www.amcfsurvey.com/article/152449.htm图3 压缩编码电路

TVP5150的AI模拟输入口与模拟摄像头输出端连接,向视频处理芯片传送模拟视频信号。模拟信号经过采样处理之后通过YOUT0~YOUT7引脚送到MPG440,采样数据在PCLK的上升沿有效,MPG440的VIDEO_CLK在收到PCLK的上升沿时获得YOUT的信号。TVP5150分场同步脉冲和行同步脉冲,分别对应其输出端VSYNC、HSYNC。MPG440正是根据与之相连的VSYNC和HSYNC信号线来实现图像的场同步和行同步操作。MPG440的视频输入数据线DATA_TV0~DATA_TV7与TVP5150的YOUT0~YOUT7相连。MPG440在接收数据的同时,将其得到的数据流传送给MPEG-4压缩编码单元,编码后的MPEG-4数据流暂存到SDRAM(2)中。MPG440片内PDMA控制器根据配置寄存器的设置准确发起对SDRAM(2)访问,同时将得到的数据流输送往HPI(主机总线接口,Host Peripherial Interface),以等待AT91RM9200通过DMA通道将数据发送到网络。

MPG440通过HPI与AT91RM9200通信,AT91RM9200将MPG440的寄存器、存储空间等资源作为其本身内存寻址访问。MPG440由AT91RM9200选通线NCS4来选通,其在AT91RM9200寻址空间中的地址段为0X50000000到0X5FFFFFFF。通过对MPG440一系列寄存器的设置,可以访问MPG440系统存储空间。MPG440中断信号RSC_INT0从通用I/O引脚的PB29输入,当缓冲器填满时,RSC_INT0引脚置低提示AT91RM9200通过DMA通道提取MPEG-4数据流。编码后视频数据读取过程和MPG440与主机通信过程由AT91RM9200读信号CFRD和写信号CFWE控制。

3.3网络模块

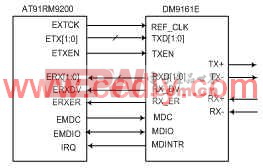

网络模块硬件设计原理如图4所示。

图4 网络模块电路

AT91RM9200的在片以太网卡端口和网络物理层芯片DM9161E的MII接口通信。发送数据时,首先置发送使能信号ETXEN有效。数据发送端ETX0~ETX1与DM9161的ETXO~ETX1引脚对应连接,作为数据发送通道,以DM9161E的时钟信号REF_CLK发送数据。数据接收端ERX 0~ERX1与DM9161E的RXDO~RXD1引脚对应连接,作为数据接收通道。管理时钟信号EMDC和管理数据输入输出信号EMDIO用来芯片控制参数的写入和读取。DM9161E的MDINTR端用来产生中断信号。

片内以太网卡通过DMA通道进行数据的发送,不影响AT91RM9200的正常运行。首先正确设置传送控制寄存器和传送地址寄存器的传送数据块字节数、数据块存储首地址等参数,随后依次从指定数据存储区地址读取1024b数据,送入内部发送缓冲器中,由MAC对数据进行封装发送,同时记录已传送字节数,直到数据块发送完毕。当发送完一组数据后,发出DMA中断请求,由AT91RM9200进行相应的处理。整个网络子系统电路由AT91RM9200控制和调度。

4.软件设计

嵌入式Linux系统主要由四个部分组成:引导内核启动的文件(bootloader)、Linux内核文件(kernel)、虚拟磁盘文件(ramdisk)、用户空间文件(user)。它们分别被放在DataFlash内的四个分区模块中。根据不同模块的具体功能采用不同的文件系统:bootloader、kernel、ramdisk,移植完成后不需要动态改变,使用较节省空间的ROMFS只读文件系统;user模块内放置一些可以动态更新的配置文件等,需要进行较多的读写操作,所以使用支持动态擦写保存的JFFS2文件系统[1]。

Linux移植技术已经成熟,本文不作详细的阐述。下文主要介绍MPEG-4压缩编码模块和CGI模块的程序设计。

评论