基于NiosⅡ的嵌入式高速逻辑分析仪

1 引言

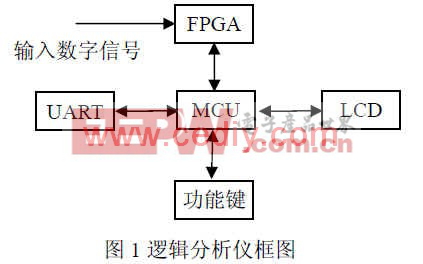

由于数字信号只有高电平和低电平两种情况,因此,用单片机 (MCU)就可直接实现多路数字信号进行采集和逻辑分析。但由于单片机的时钟频率较低,完成一次采样的时间受程序执行指令速度的限制,采样速率通常不超过 1MHz。因此,用单片机只能实现对低速率数字信号进行逻辑分析。FPGA的工作时钟速率通常可达 200MHz以上,可对高速数字信号进行采样,但普通的 FPGA在与外部设备进行数据交换时显得不灵活。为了解决上述问题,通常是将 MCU与 FPGA结合起来,用 FPGA对高速数字信号进行采样,用 MCU负责与外部设备进行数据交换,从而实现对高速数字信号进行逻辑分析,如图 1所示。

随着可编程逻辑器件的发展,Altera公司研发了可以嵌入软 CPU核的 Cyclone系列和 Stratix系列的 FPGA芯片。嵌入式软核与普通硬核的昀大差别在于它的可裁减性,设计者可根据设计需求定制出不同结构的软核处理器。软 CPU核的嵌入实现了 CPU与 FPGA的无缝连接,使芯片既能处理高速数字信号,又能方便灵活地与芯片外部设备进行数据交换,还增加了系统的集成度和可靠性。

2 定制软 CPU核

软核的定制要利用 Altera公司提供的 SOPC Builder软件。

2.1定制 NiosⅡ处理器早期的软核处理器是 Nios,但其稳定性不够好,现已被 NiosⅡ所替代。 NiosⅡ处理器有三种类型: e(经济型 )、s(标准型)和 f(增强型)。选择不同类型的处理器所占用的逻辑资源和存储器资源大小不同,处理器的运算速度处理能力也有所差别。

2.2定制片内 RAM

片内 RAM作为软核程序的运行空间,对于没有扩展外部存储器的设计,片内 RAM是必须的部分。通过软件设计向导,可以设置片内存储器的类型,大小,以及初始化文件。 Cyclone系列芯片有 13~64个片内 RAM块,每个 RAM块的大小是 4K(128字×36位),用户可根据需要设置存储器的字数和字长。当定义的字数超过 128时,多个 RAM块可组成在一起,构成更大容量的存储器,满足设计要求。

2.3定制 UART接口

UART接口是软核与计算机通信的主要接口,通过设计向导可定制 UART接口。在定制 UART接口时,可以设置其波特率,校验位,是否允许 DMA控制。通过此基本设置,软核可以与 PC机之间实现串口通信的功能。

2.4定制 LCD控制端口和键盘控制端口此类端口是普通 I/O端口,设置比较简单。需要注意的是 LCD的数据端口是 8位的双向端口。当定制了以上 4部分后,即可生成软 CPU核。

3 最小系统形成

完成定制软核后,需要对软核编程,形成基于软核的昀小系统。

对软核的编程在 Nios ⅡIDE环境下进行。首先利用软件生成针对某软核的模版程序,用户程序都可以从模版开始。在生成模版程序的同时,也形成了 system.h文件,此文件中包含了对用户编程有用的许多信息,包括所有端口的地址空间分配,中断号等。在文件 altera_avalon_pio_regs.h中包含了对普通 I/O端口进行读写操作的函数,通过对函数的调用可实现对端口的操作。在文件 altera_avalon_uart_regs.h中包含了对 UART操作的基础函数,对串口的所有操作,都可通过对此中函数的调用来完成。

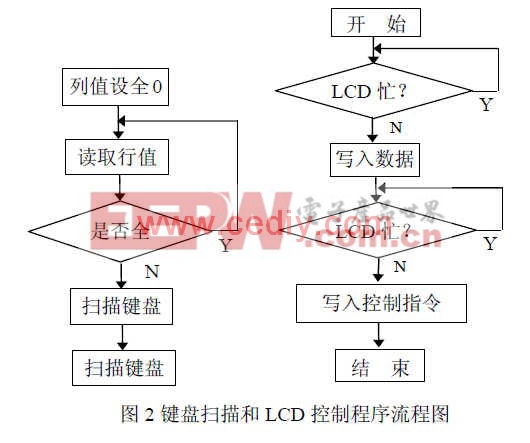

在昀小系统中,实现软核对 LCD的数据交换,读取键盘值,以及与计算机之间的通信。本设计键盘使用 4*4键盘,显示器采用 240*128点阵 LCD显示模块。主要子程序流程图如图 2所示。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论