基于CPLD译码的DSP二次Bootloader方法

随着数字信号处理技术的快速发展,数字信号处理器(DSP)越来越广泛地应用于各种实时嵌入式系统中。当系统调试完毕,想脱离仿真环境并在上电复位后自动启动程序代码运行时,必须将程序代码存储在非易失性存储器中。Flash存储器以其大容量和可在线编程等特点已成为DSP系统的一个基本配置。在系统上电复位后,DSP芯片内部固化的引导装载器(Bootloader)把应用程序从Flash引导到DSP芯片内高速 RAM中执行。这样既利用了外部存储器扩展DSP有限的ROM资源,又可以充分保证用户程序的全速运行[1-2]。

本文采用公司的16位定点DSP芯片TMS320VC5509A(以下简称5509A),其PGE封装形式只有14根地址总线(A0~A13),最大只能寻址16KB的Flash存储器[3]。若要寻址更大地址空间,就需要控制Flash存储器的高位地址线。常见的解决方案是采用DSP的通用输入输出GPIO(General Purpose Input/Output)引脚来控制Flash的高位地址线,从而实现Flash存储器的分页访问[5-6]。然而,对于较大容量的Flash存储器,如本文采用的Am29LV800的容量为512K×16bit,有19根地址线[4],如果采用上述方法,硬件连接虽然简单,但会占用较多的GPIO引脚,而且以后的系统扩展也不方便。本文介绍了一种基于CPLD快速译码的DSP二次引导方法,利用CPLD的时序严格、译码速度快、可在线编程等特点,在 DSP的外部存储器接口EMIF(Exteral Memory Interface)的CE2空间模拟了一个Flash换页寄存器FPR(Flash Page Register),在上电复位后控制Flash的高位地址线,从而实现Flash的分页访问。因此,可通过二次bootloader程序修改FPR的值,控制Flash的高位地址线,将最终的应用程序加载到RAM中运行。

1 TMS320VC5509A的并行引导模式

1.1 5509A的引导模式

5509A的引导模式选择是通过4个模式选择引脚BOOTM[3:0]来配置的,BOOTM3~0引脚分别与GPIO0、3、2、1相连。5509A提供了六种引导模式,即EHPI引导模式、8位/16位并行EMIF引导模式、8位/16位标准串行口引导模式、SPI EEPROM引导模式、USB引导模式以及I2C E2PROM引导模式。本文采用16位并行EMIF引导模式,将BOOTM[3:0]设置为1011即可。

在16位并行EMIF引导模式下,DSP芯片内部固化的Bootloader程序上电复位后,首先从CE1空间首地址0x200000h处开始读取程序代码,并加载到RAM中运行。

1.2 5509A的引导表格式

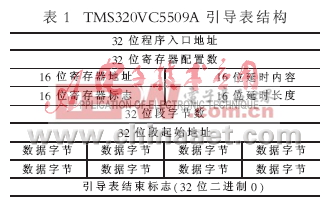

程序代码以引导表的格式存储在Flash存储器中。引导表是独立于所选引导模式的一种特定的格式,包含了用户程序的代码段、数据段、段在RAM中的目标地址以及程序入口地址等其他相关信息。5509A引导表结构如表1所示。

DSP芯片内部固化的Bootloader的主要功能是将Flash中存储的引导表按一定顺序加载到 RAM中,然后跳转到32位程序入口地址开始执行。引导表文件可以通过TI公司提供的16进制转换工具生成,一般是hex格式,然后将此hex文件烧写到 Flash存储器中供Bootloader加载。

2 DSP二次Bootloader的原理及实现

由上述分析可知,DSP用户程序的并行加载过程是由DSP内固化的Bootloader实现的。由于5509A的PGE封装只有14根地址线,最多只能访问到16K×16bit地址空间。对于超过16KB的用户代码,Bootloader将不能加载全部的引导表文件。因此若要加载超过16K的用户代码,必须进行二次Bootloader。

评论