嵌入式系统中DRAM控制器的CPLD解决方案

存储器是嵌入式计算机系统的重要组成部分之一。通常采用静态存储器,但是在系统需要大容量存储器的情况下,这种方式将使成本猛增。如果采用DRAM存储器,则可以大幅度降低系统设计成本;但DRAM有复杂的时序要求,给系统设计带来了很大的困难。

本文引用地址:http://www.amcfsurvey.com/article/152121.htm为了方便地使用DRAM,降低系统成本,本文提出一种新颖的解决方案:利用80C186XL的时序特征,采用CPLD技术,并使用VHDL语言设计实现DRAM控制器。

一、80C186XL RCU单元的资源

80C186XL的BIU单元提供20位地址总线,RCU单元也为刷新周期提供20位地址总线。80C186XL能够产生刷新功能,并将刷新状态编码到控制信号中。

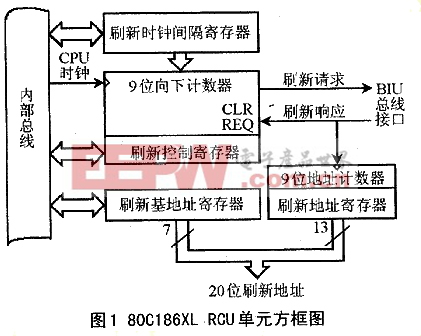

图1是RCU单元的方框图。它由1个9位递减定时计数器、1个9位地址计数器、3个控制寄存器和接口逻辑组成。当RCU使能时,递减定时计数器每一个CLKOUT周期减少1次,定时计数器的值减为1时,则产生刷新总线请求,递减定时计数器重载,操作继续。刷新总线周期具有高优先级,旦80C186XL总线有空,就执行刷新操作。

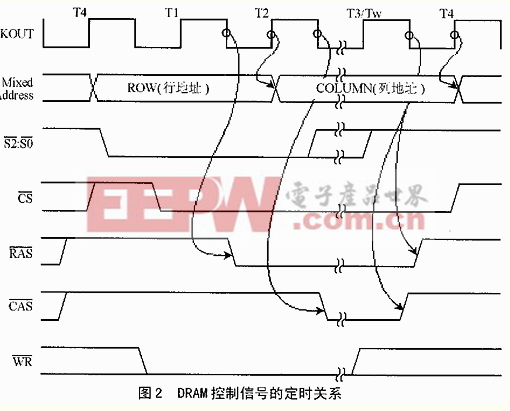

设计者可将刷新总线周期看成是“伪读”周期。刷新周期像普通读周期一样出现在80C186XL总线上,只是没有数据传输。从引脚BHE/RFSH和A0的状态可以判别刷新周期,如表1所列。刷新总线周期的时序要求如图2所示。

表1 刷新周期的引脚状态

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论