使用DP83640实现标准网络IEEE1588的同步

1.0 简介

美国国家半导体的DP83640精密PHYTER?实现了IEEE 1588精密时间协议(PTP)的时钟关键部分,允许高精度 IEEE 1588节点实现。当使用包含IEEE1588功能器件、边界时钟和透明时钟的网络时,利用非常简单的时钟伺服算法 来确定速率调整和时间校正,可以获得非常高的精度。不需 要复杂处理,只需要对协议测量进行简单平均或滤波即可。 当网路由不具有IEEE 1588能力的器件构成时,包延时偏差 (PDV)就很重要。简单时钟伺服不会提供很高精度的同 步。

本文描述了一种同步方法,它可以为较大PDV系统带 来更高的同步精度。这里描述的方法试图检测最小延时,或 “幸运包”。这个方法还利用了DP83640时钟控制机理来独 立控制时钟速率和时间校正,从而将时钟时间精度内的过冲 和摆动降低到最小。

2.0 背景

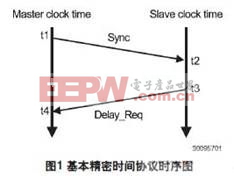

IEEE1588精确时间协议给从机提供了基本信息,用以确 定相对于最高级主时钟的频率以及时间偏差。基本算法包括 使用各自的同步和延时请求消息来测量主机到从机之间和从 机到主机的路径延时。 图1显示了最基本的IEEE 1588的时序图。

主机到从机和从机到主机的延时为:

MSdelay = t2 - t1

SMdelay = t4 Ct3

单向延时或称为平均路径延时正是这两个延时的平均值

MeanPathDelay = (MSdelay + SMdelay)/2

理想情况下,时间偏移为:

offset_from_master = MSdelay C meanPathDelay

在包含支持IEEE-1588网络元件(桥、开关、路由器)的网络中,包延时偏差基本上可以忽略。在边界时钟器件中,同步时钟在网络元件上得以保持,它与上游主机同步时间和速率,并充当下游器件的主机。在透明时钟器件中,因为PTP报文要经过这个器件,所以通过测量其停留时间来校 正包延时偏差。

在无1588能力的网络中不做补偿,导致包延时变量大概 是几十或几百微妙的数量级。这些延时变得非常明显,使得 单一测量极度不正确。

在使用只有简单平均和滤波的基本算法的单开关条件 下,得到了图2在80%流量条件下的MTIE(最大时间间隔误差)测试波形。很容易看到,这种方法提供了相对较差的同 步,其误差达到100ms之大。

2.1 建议算法

在无1588能力元件的网络中,包延时可能在每个器件 的最小物理延时和通过每个器件的最大延时总和的范围内变 化。实践中,每个设备经常会有最小传输延时,因此主机到 从机产生最小的总包延时。基本操作是尝试检测最小延时, 或者“幸运延时”,利用这些包的结果进行速率和时间校 正。算法基本上可分为三级:平均路径延时测量、速率校正 和时间校正。

2.1.1 平均路径延时测量

在大多数网络中,最小路径延时是相对恒定的值。再 次配置网络能够引起步长变化,但是这种配置并不是经常性 的。因此有可能采用长期跟踪最小环回延时(即全部的同步 延时请求计算)的方式来检测最小平均路径。这种方法保持 最后N个平均路径延时测量记录,并从中找到最小值:

Min_meanPathDelay(n) = min(meanPathDelay[n+1-N:n]

其中,Min_meanPathDelay(n)为第n次测量记录中保留的N个数据中的最小值。

进行速率校正和时间校正时确定最小平均路径是关键。

评论