高速异步FIFO的设计与实现

现代集成电路芯片中,随着设计规模的不断扩大.一个系统中往往含有数个时钟。多时钟带来的一个问题就是,如何设计异步时钟之间的接口电路。异步FIFO(First In First Out)是解决这个问题的一种简便、快捷的解决方案。使用异步FIFO可以在两个不同时钟系统之间快速而方便地传输实时数据.在网络接口、图像处理等方面,异步FIFO都得到广泛的应用。异步FIFO是一种先进先出的电路,使用在数据接口部分,用来存储、缓冲在两个异步时钟之间的数据传输。在异步电路中,由于时钟之间周期和相位完全独立,因而数据的丢失概率不为零。如何设计一个可靠性高、速度高的异步FIFO电路便成为一个难点。

本文引用地址:http://www.amcfsurvey.com/article/151917.htm1 异步FIFO的工作原理及逻辑框图

本文根据实际工作的需要.给出了一种利用片内RAM构造FIFO器件的设计,重点强调了设计有效.可靠的握手信号FULL和EMPTY的方法。并在LATTICE公司的FPGA芯片LFXP2-5E上实现。LFXP2-5E属于LATIICE公司XP2系列的一款,他采用优化的FlexiFLASH结构。内部包含有基于查找表的逻辑、分布式和

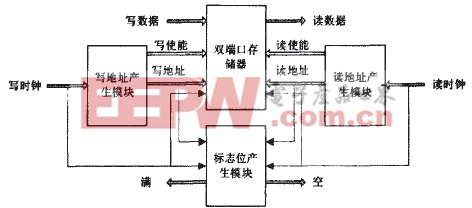

由图1可以看出:异步FIFO一般由四个模块构成:数据存储单元,写地址产生模块,读地址产生模块,标志位产生模块。整个系统分为两个完全独立的时钟域―读时钟域和写时钟域:在写时钟域部分由写地址产生逻辑产生写控制信号和写地址:读时钟域部分,由读地址产生逻辑产生读控制信号和读地址;在标志位产生模块部分,由读写地址相互比较产生空/满标志。异步FIFO的操作过程为:在写时钟的上升沿.当写使能有效时,将数据写入到双口RAM中写地址对应的位置中:在读时钟的上升沿,当读使能有效时。则按先进先出顺序读出数据。在FIFO写满或读空的情况下。分别对满标志FuLL或空标志EMPTY信号置位。来表示FIFO的两种特殊状态。

图1异步FIFO逻辑框图

2 异步FIFO的VHDL实现读时钟

2.1 FIFO设计的难点

如何同步异步信号,使触发器不产生亚稳态是设计异步FIFO的难点。国内外解决此问题的较成熟办法是对写地址膜地址采用格雷码,本文也直接采用格雷码。异步FIFO设计的另一个难点是如何判断FIFO的空/满状态。为了保证数据正确的写入或读出。必须保证异步FIFO在满的状态下.不能进行写操作:在空的状态下不能进行读操作。通常情况下将存储器组织成一个环形链表。

满/空标志产生的原则是:写满不溢出.读空不多读。即无论在什么情况.都不应出现读写地址同时对一个存储器地址操作的情况。在读写地址相等或相差一个或多个地址的时候,满标志应该有效。表示此时FIFO已满,外部电路应停止对FIFO发数据。在满信号有效时写数据应根据设计的要求,或保持、或抛弃重发。同理,空标志的产生也是如此。为了更好的判断满/空标志。采用在FIFO原来深度的基础上增加一位的方法,而由该位组成的格雷码并不代表新的地址。也就是说3位格雷码可表示8位的深度,若再加一位最高位MSB,则这一位加其他三位组成的格雷码并不代表新的地址,也就是说格雷码的0100表示7,而1100仍然表示7,只不过格雷码在经过一个以0位MSB的循环后进入一个以1为MSB的循环,然后又进入一个以0位MSB的循环。其他的三位码仍然是格雷码。举例说明:一个深度为8字节的FIFO怎样工作(使用已转换为二进制的指针),N=3,指针宽度为N+I=4。开始rd_ptr_bin和wr_ptr_bin均为“0000”。此时FIFO中写入8个字节的数据。wr_ptr_bin=“1000,rd_ptr_bin=“0000”。当然,这就是满条件。现在,假设执行了8次的读操作.使得rd_ptr_bin=“1000”,这就是空条件。另外的8次写操作将使wr_ptr_bin等于“0000”,但rd_ptr_bin仍然等于“1000”,因此,FIFO为满条件。

由以上可知。满标志的产生条件为:写指针赶上读指针.即写满后,又从零地址开始写直到赶上读指针,这时期读写指针的最高位不同,其他位相同,这就是满条件。空标志的产生条件为:复位或者是读指针赶上写指针.即在写指针循环到第二轮时读指针赶上写指针,这时读写指针的高低位均相同,这就是空条件。

2.2异步F1F0的VHDL语言实现

以下为本程序的核心部分

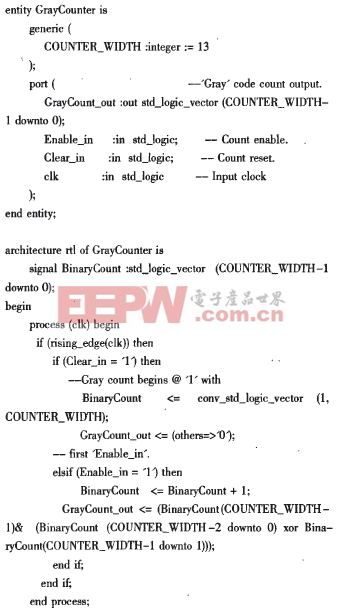

程序1格雷码计数器的实现

评论