采用VC++程序的FPGA重配置设计方案

结合对

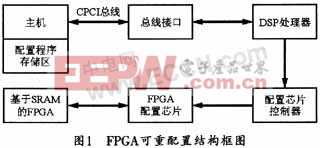

图1中借用原系统DSP处理器的控制功能来完成上位机控制命令及下载数据的接收,上位机与系统之间采用PCI总线接口。上位机命令由DSP处理器进行解析,并随后发送到配置芯片控制器中,配置芯片控制器可由CPLD器件构成,它的编程采用EEPROM或FLASH技术,且无需外部存储器芯片。

在设计中,上位机通过PCI总线建立通信并发送配置命令及数据至DSP,DSP以串行方式通知配置芯片控制器发送控制命令以及要进行配置的数据包,同时,配置芯片控制器在解析命令后,还应执行相应的操作,并完成FPGA配置芯片所需的下载时序及配置数据。配置芯片的数据下载过程称为编程操作,编程完成后,再启动配置操作,即可进行FPGA从配置芯片读取新的系统配置程序过程。与常用的FPGA配置方法相比较,本文所采用的FPGA可重构设计的硬件结构更加简单,用户操作也更加方便,而且在对FPGA的配置芯片写入配置程序数据的时候,并不会影响到FPGA的继续工作,系统重构的时隙也更小。

用户发送配置数据流到EPCS对FPGA进行配置的结构图如图2所示,其中PC机部分为上位机配置控制的用户软件宿主。配置控制软件主要包括用户应用程序(Win32应用程序)、仪器驱动程序、总线驱动程序三部分,总线驱动位于整个软件系统的最底层,可通过硬件抽象层(HAL)直接与硬件进行交流。仪器驱动位于总线驱动和用户应用程序之间。它对上可为屏蔽底层工作细节提供应用程序调用的接口函数,对下则可发送命令或接收数据。用户应用程序则位于软件结构的最上层,可通过调用仪器驱动程序,间接地与底层进行交互。其结构图如图3所示。

评论