基于SoPC的通用在线调试器设计

目前,国内生产的部分在线仿真调试器可以对部分嵌入式芯片进行仿真调试。但从本质上,这些仿真调试器无法对所有带在线调试功能的嵌入式芯片进行仿真调试。BDI2000和TRACE32等仿真器可以在不改变硬件条件下,通过下载针对特定嵌入式芯片的调试“核”来实现对不同嵌入式芯片的仿真调试,但是非常昂贵,难以适应国内绝大多数中小企业的实际需求。

本文基于SOPC软硬件协调设计验证技术设计了一款通用在线调试器。SOPC技术将传统的在线调试器以芯片形式呈现,采用知识产权核(IP core)复用技术,抽象各种不同架构的嵌入式处理器接口,给出支持统一调试接口的IP core架构,提出了基于通用在线调试器的嵌入式软件调试方法。

本文介绍了系统架构,以及关键子系统的工作原理及其与所处硬件环境之间的交互,最后对JTAG IP core子系统进行了仿真验证。

1 整体设计

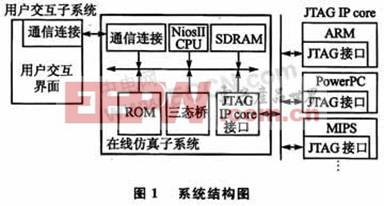

系统由用户交互、在线仿真和JTAG IP core三个子系统构成,如图1所示。

用户交互子系统包括TCP/IP通信端口与用户交互界面。它主要负责访问和处理源文件;接收调试命令,根据TCP/IP协议封装成调试命令请求包,发送给通用调试器;同时,解析目标机的响应。其中,通信端口负责与通用在线调试器通信。

在线仿真子系统是一个针对不同类型嵌入式处理芯片的高扩展性嵌入式系统。它包括硬件部分和软件部分。硬件部分采用SOPC技术加载Altera公司的IP core形成一个以NiosII CPU为核心的,TCP/IP和JTAG IP core端口为通信模块的硬件平台。软件部分包括网络传输处理和JTAG IP core接口程序部分。

JTAG IP core是业务信号处理逻辑模块,可以是ARM、PowerPC、MIPS等不同架构的嵌入式处理器。

1.1 核心子系统设计

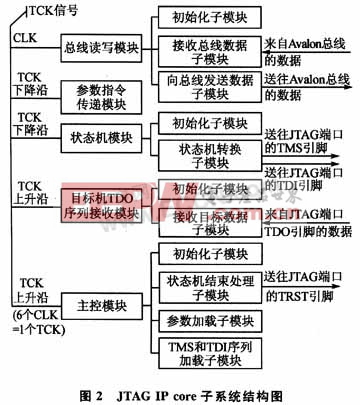

JTAG IP core是系统的核心部分。它负责目标机调试命令的格式转换、传送逻辑控制,以及JTAG状态机状态转换的控制。JTAG IP core子系统划分为5个模块,每个模块又由子模块所构成。模块的执行次序不同,或并发,或顺序执行。JTAG IP core子系统结构图如图2所示。

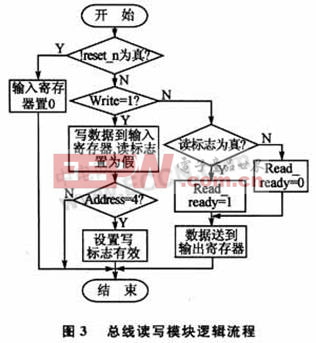

总线读写模块负责接收参数和指令,同时将处理后的数据输出到总线。接收总线数据子模块接收Avalon总线的数据并更新标志位;读信号触发向总线发送数据子模块进行数据传输。总线读写模块逻辑流程如图3所示。

评论