基于FPGA的片上系统和嵌入式系统的远程监控系统

本系统立足于利用Intemet实现核环境信息的远程采集。在实现上,采用了基于SOPC技术的嵌入式解决方案,通过在FPGA中嵌入NioslI软核处理器和所需外设的IP Core(硅知识产权核),然后再配备相应的网络接口,实现利用互联网进行信息的传输。

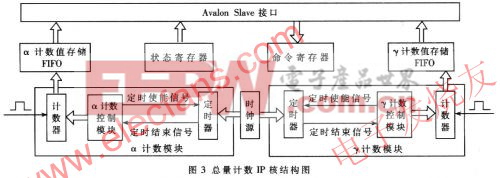

本文引用地址:http://www.amcfsurvey.com/article/151480.htm另外,通过开发用于控制信息采集子系统的IP核,利用FPGA固有的硬件并行特性,本系统做到了对多个信息源进行真正意义上的并行监控,即在进行α射线探测的同时也可以进行γ射线和温湿度等信息的获取。

1 系统硬件设计及实现

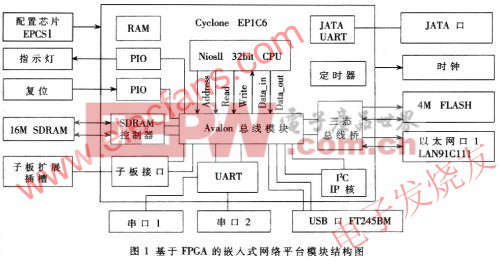

在本系统的设计中,硬件上为了做到通用性,在结构上划分为两部分,即用于完成现场监控和数据远程传输的通用网络平台和用于完成温湿度、液位、α及γ辐射总量测量等工作的环境信息采集子系统。其结构分别如图l、图2所示。两个子系统通过一条40芯扁平电缆连接。在软件上,考虑到利用互联网进行远程数据传输的复杂性,使用嵌入式操作系统和TCP/IP协议栈是必然的选择,因此硬件上也围绕这个关键点进行设计。

1.1 Niosii软核CPU

NiosII软核CPU是A137ERA公司推出的一种通用32位RISC嵌入式处理器,它特别为可编程逻辑进行了优化设计,并配备有功能完善的开发套件,包括C/C++编译器、集成开发环境(IDE)、JTAG调试器等,是ALTERA公司可编程单芯片系统解决方案的核心。

作为一个软核处理器,NiosII提供了可配置的硬件及软件调试特性,包括基本的JTAG的运行控制(运行、停止、单步、存储器等)、硬件断点、数据触发、片内和片外跟踪、嵌入式逻辑分析仪。这些强大的工具可以在开发阶段使用,调试通过后便可以去掉,节省资源。NiosII处理器还提供了高、中、低三种不同性能的内核,通过与ALTERA提供的超过60种IP核(UART、时钟、DMA、SDRAM、并行I/0等)结合使用,设计师可以方便地针对特定的应用创建一个在处理器、外设、存储器和I/O接口方面都完美的方案。除此以外,NiosII还有很多其他优秀的特性,如指令定制、硬件加速器等。

1.2 网络接口单元

以太网接口芯片采用了SMSC公司专门用于嵌入式产品的LAN91C111快速以太网控制器。该芯片内部同时集成了以太网介质访问控制器(MAC)及物理层收发器(PHY),支持10/100M全双工传输模式、自动协商及流控等功能。其主机接口具有同步总线、异步总线等多种工作模式,可以方便地与各种体系的CPU连接。本设计中使用了异步总线接口模式,并与FLASH共用地址线和数据线,通过FPGA上的适配模块连接到Avalon片内总线。

1.3 存储器单元

由于存储操作系统内核、应用程序代码、程序数据等的需要,本系统使用了一片型号为AM29LV320D的FLASH芯片。该芯片由AMD公司推出,容量为4MB,支持CFI接口,其与AvMon总线的连接需要FPGA内部的总线适配模块进行时序匹配。SDRAM用于存储运行期的程序代码和数据,HY57V563220B(L)T为现代公司推出的容量达16MB的SDRAM,由于该芯片端口宽度可达32位,因此系统中使用单芯片即可。SDRAM读写时序比较复杂,需要在FPGA中集成专用的SDRAM控制器IP核与其对接。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论